6.1 تعارف

جدید عام مقصد کے کمپیوٹر دو قسم کے ہیں: CISC اور RISC۔ CISC کا مطلب ہے کمپلیکس انسٹرکشن سیٹ کمپیوٹر۔ RISK کا مطلب ہے کم شدہ انسٹرکشن سیٹ کمپیوٹر۔ 6502 یا 6510 مائکرو پروسیسرز، جیسا کہ کموڈور-64 کمپیوٹر پر لاگو ہوتا ہے، CISC فن تعمیر سے زیادہ RISC فن تعمیر سے مشابہت رکھتا ہے۔

RISC کمپیوٹرز میں عام طور پر CISC کمپیوٹرز کے مقابلے میں اسمبلی زبان کی چھوٹی ہدایات (بائٹس کی تعداد کے لحاظ سے) ہوتی ہیں۔

نوٹ : چاہے CISC، RISC، یا پرانے کمپیوٹر سے نمٹنا ہو، ایک پیریفیرل اندرونی بندرگاہ سے شروع ہوتا ہے اور کمپیوٹر کے سسٹم یونٹ (بیس یونٹ) کی عمودی سطح پر ایک بیرونی بندرگاہ سے ہوتا ہوا بیرونی آلہ تک جاتا ہے۔

CISC کمپیوٹر کی ایک عام ہدایت کو دیکھا جا سکتا ہے جیسے اسمبلی کی کئی مختصر ہدایات کو ایک طویل اسمبلی لینگویج انسٹرکشن میں شامل کرنا جس کے نتیجے میں آنے والی ہدایات کو پیچیدہ بناتا ہے۔ خاص طور پر، ایک CISC کمپیوٹر آپرینڈز کو میموری سے مائیکرو پروسیسر رجسٹر میں لوڈ کرتا ہے، ایک آپریشن کرتا ہے، اور پھر نتیجہ واپس میموری میں محفوظ کرتا ہے، یہ سب کچھ ایک ہی ہدایات میں ہوتا ہے۔ دوسری طرف، یہ RISC کمپیوٹر کے لیے کم از کم تین ہدایات (مختصر) ہیں۔

سی آئی ایس سی کمپیوٹرز کی دو مشہور سیریز ہیں: انٹیل مائکرو پروسیسر کمپیوٹرز اور اے ایم ڈی مائکرو پروسیسر کمپیوٹر۔ AMD کا مطلب ہے ایڈوانسڈ مائیکرو ڈیوائسز؛ یہ ایک سیمی کنڈکٹر مینوفیکچرنگ کمپنی ہے۔ انٹیل مائیکرو پروسیسر سیریز، ترتیب کے لحاظ سے، 8086, 8088, 80186, 80286, 80386, 80486, Pentium, Core, i Series, Celeron, and Xeon ہیں۔ ابتدائی انٹیل مائکرو پروسیسرز جیسے 8086 اور 8088 کے لیے اسمبلی کی زبان کی ہدایات زیادہ پیچیدہ نہیں ہیں۔ تاہم، وہ نئے مائکرو پروسیسرز کے لیے پیچیدہ ہیں۔ CISC سیریز کے حالیہ AMD مائیکرو پروسیسرز رائزن، آپٹرون، ایتھلون، ٹوریون، فینوم اور سیمپرون ہیں۔ انٹیل اور اے ایم ڈی مائکرو پروسیسرز کو x86 مائکرو پروسیسرز کے نام سے جانا جاتا ہے۔

ARM کا مطلب ہے ایڈوانسڈ RISC مشین۔ اے آر ایم آرکیٹیکچرز RISC پروسیسرز کے خاندان کی وضاحت کرتے ہیں جو ایپلی کیشنز کی وسیع اقسام میں استعمال کے لیے موزوں ہیں۔ جب کہ ڈیسک ٹاپ پرسنل کمپیوٹرز میں بہت سے Intel اور AMD مائیکرو پروسیسر استعمال کیے جاتے ہیں، بہت سے ARM پروسیسرز حفاظتی اہم نظاموں میں ایمبیڈڈ پروسیسرز کے طور پر کام کرتے ہیں جیسے آٹوموٹیو اینٹی لاک بریک اور سمارٹ واچز، پورٹیبل فونز، ٹیبلٹس اور لیپ ٹاپ کمپیوٹرز میں عام مقصد کے پروسیسرز کے طور پر۔ . اگرچہ دونوں قسم کے مائیکرو پروسیسر چھوٹے اور بڑے آلات میں دیکھے جا سکتے ہیں، لیکن RISC مائیکرو پروسیسرز بڑے آلات کے مقابلے چھوٹے آلات میں زیادہ پائے جاتے ہیں۔

کمپیوٹر ورڈ

اگر کسی کمپیوٹر کو 32 بٹس ورڈ کا کمپیوٹر کہا جائے تو اس کا مطلب ہے کہ معلومات کو مدر بورڈ کے اندرونی حصے میں بتیس بٹ بائنری کوڈز کی شکل میں محفوظ، منتقل اور ہیر پھیر کیا جاتا ہے۔ اس کا مطلب یہ بھی ہے کہ کمپیوٹر کے مائیکرو پروسیسر میں عام مقصد کے رجسٹر 32 بٹ چوڑے ہیں۔ 6502 مائکرو پروسیسر کے A، X، اور Y رجسٹر عام مقصد کے رجسٹر ہیں۔ وہ آٹھ بٹ چوڑے ہیں، اور اس لیے کموڈور-64 کمپیوٹر آٹھ بٹ لفظ والا کمپیوٹر ہے۔

کچھ الفاظ

X86 کمپیوٹرز

x86 کمپیوٹرز کے لیے بائٹ، لفظ، ڈبل ورڈ، کواڈ ورڈ اور ڈبل کواڈ ورڈ کے معنی درج ذیل ہیں۔

- بائٹ : 8 بٹس

- کلام : 16 بٹس

- دوہرا لفظ : 32 بٹس

- Quadword : 64 بٹس

- ڈبل کواڈ ورڈ : 128 بٹس

اے آر ایم کمپیوٹرز

ARM کمپیوٹرز کے لیے بائٹ، ہاف ورڈ، لفظ اور ڈبل ورڈ کے معنی درج ذیل ہیں۔

- بائٹ : 8 بٹس

- آدھا ہو جانا : 16 بٹس

- کلام : 32 بٹس

- دوہرا لفظ : 64 بٹس

x86 اور ARM ناموں (اور قدروں) کے لیے فرق اور مماثلت کو نوٹ کیا جانا چاہیے۔

نوٹ : کمپیوٹر کی دونوں اقسام میں علامتی عدد دو کے تکمیلی ہیں۔

میموری کا مقام

کموڈور-64 کمپیوٹر کے ساتھ، میموری کی جگہ عام طور پر ایک بائٹ ہوتی ہے لیکن پوائنٹرز (بالواسطہ ایڈریسنگ) پر غور کرتے وقت کبھی کبھار لگاتار دو بائٹس ہو سکتی ہے۔ ایک جدید x86 کمپیوٹر کے ساتھ، 16 بائٹس (128 بٹس) کے ڈبل کواڈ ورڈ کے ساتھ کام کرتے وقت میموری لوکیشن 16 لگاتار بائٹس، 8 بائٹس (64 بٹس) کے کواڈ ورڈ کے ساتھ ڈیل کرتے وقت لگاتار 8 بائٹس، ڈبل ورڈ کے ساتھ کام کرتے وقت لگاتار 4 بائٹس۔ 4 بائٹس (32 بٹس)، 2 لگاتار بائٹس جب 2 بائٹس (16 بٹس) کے لفظ کے ساتھ کام کرتے ہیں، اور بائٹ (8 بٹس) کے ساتھ کام کرتے وقت 1 بائٹ۔ ایک جدید اے آر ایم کمپیوٹر کے ساتھ، میموری لوکیشن 8 بائٹس (64 بٹس) کے ڈبل ورڈ کے ساتھ نمٹتے وقت لگاتار 8 بائٹس، 4 بائٹس (32 بٹس) کے ایک لفظ کے ساتھ کام کرتے وقت لگاتار 4 بائٹس، آدھے لفظ کے ساتھ کام کرتے وقت لگاتار 2 بائٹس۔ 2 بائٹس (16 بٹس)، اور بائٹ (8 بٹس) کے ساتھ کام کرتے وقت 1 بائٹ۔

یہ باب وضاحت کرتا ہے کہ CISC اور RISC فن تعمیر میں کیا مشترک ہے اور ان میں کیا فرق ہے۔ یہ 6502 µP اور کموڈور-64 کمپیوٹر کے مقابلے میں کیا جاتا ہے جہاں یہ لاگو ہوتا ہے۔

6.2 جدید پی سی کا مدر بورڈ بلاک ڈایاگرام

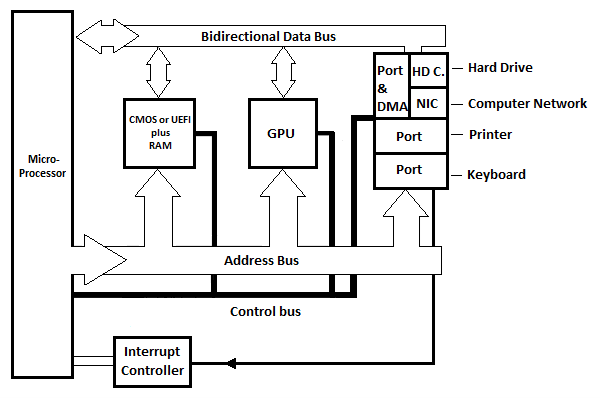

PC کا مطلب ہے پرسنل کمپیوٹر۔ پرسنل کمپیوٹر کے لیے سنگل مائیکرو پروسیسر والے جدید مدر بورڈ کے لیے ذیل میں ایک عام بنیادی بلاک ڈایاگرام ہے۔ یہ CISC یا RISC مدر بورڈ کی نمائندگی کرتا ہے۔

تصویر 6.21 جدید پی سی کا بنیادی مدر بورڈ بلاک ڈایاگرام

خاکہ میں تین اندرونی بندرگاہیں دکھائی گئی ہیں، لیکن عملی طور پر اور بھی ہیں۔ ہر بندرگاہ میں ایک رجسٹر ہوتا ہے جسے خود بندرگاہ کے طور پر دیکھا جا سکتا ہے۔ ہر پورٹ سرکٹ میں کم از کم ایک اور رجسٹر ہوتا ہے جسے 'سٹیٹس رجسٹر' کہا جا سکتا ہے۔ اسٹیٹس رجسٹر اس پروگرام کی پورٹ کی نشاندہی کرتا ہے جو مائکرو پروسیسر کو انٹرپٹ سگنل بھیج رہا ہے۔ ایک انٹرپٹ کنٹرولر سرکٹ ہے (نہیں دکھایا گیا) جو مختلف بندرگاہوں سے مختلف انٹرپٹ لائنوں کے درمیان فرق کرتا ہے اور اس کی µP تک صرف چند لائنیں ہیں۔

تصویر میں HD.C کا مطلب ہارڈ ڈرائیو کارڈ ہے۔ NIC کا مطلب ہے نیٹ ورک انٹرفیس کارڈ۔ ہارڈ ڈرائیو کارڈ (سرکٹ) ہارڈ ڈرائیو سے جڑا ہوا ہے جو جدید کمپیوٹر کے بیس یونٹ (سسٹم یونٹ) کے اندر ہے۔ نیٹ ورک انٹرفیس کارڈ (سرکٹ) ایک بیرونی کیبل کے ذریعے دوسرے کمپیوٹر سے منسلک ہوتا ہے۔ خاکہ میں، ایک پورٹ اور ایک DMA ہے (مندرجہ ذیل مثال کو دیکھیں) جو ہارڈ ڈسک کارڈ اور/یا نیٹ ورک انٹرفیس کارڈ سے جڑے ہوئے ہیں۔ ڈی ایم اے کا مطلب ہے براہ راست میموری تک رسائی۔

کموڈور-64 کمپیوٹر باب سے یاد رکھیں کہ میموری سے بائٹس کو ڈسک ڈرائیو یا کسی دوسرے کمپیوٹر پر بھیجنے کے لیے، ہر بائٹ کو متعلقہ اندرونی پورٹ پر کاپی کرنے سے پہلے مائیکرو پروسیسر کے رجسٹر میں کاپی کرنا پڑتا ہے، اور پھر خود بخود ڈیوائس کو. میموری میں ڈسک ڈرائیو یا کسی دوسرے کمپیوٹر سے بائٹس وصول کرنے کے لیے، میموری میں کاپی کرنے سے پہلے ہر بائٹ کو متعلقہ اندرونی پورٹ رجسٹر سے مائکرو پروسیسر رجسٹر میں کاپی کرنا ہوگا۔ اگر ندی میں بائٹس کی تعداد زیادہ ہو تو اس میں عام طور پر زیادہ وقت لگتا ہے۔ تیزی سے منتقلی کا حل مائکرو پروسیسر سے گزرے بغیر ڈائریکٹ میموری ایکسیس (سرکٹ) کا استعمال ہے۔

ڈی ایم اے سرکٹ پورٹ اور ایچ ڈی کے درمیان ہے۔ سی یا این آئی سی۔ DMA سرکٹ کی براہ راست میموری تک رسائی کے ساتھ، بائٹس کے بڑے سلسلے کی منتقلی DMA سرکٹ اور میموری (RAM) کے درمیان مائکرو پروسیسر کی مسلسل شرکت کے بغیر ہوتی ہے۔ DMA ایڈریس بس اور ڈیٹا بس کو µP کی جگہ استعمال کرتا ہے۔ منتقلی کی کل مدت اس سے کم ہے اگر µP مشکل استعمال کی جائے۔ HD C. یا NIC دونوں DMA استعمال کرتے ہیں جب ان کے پاس RAM (میموری) کے ساتھ منتقلی کے لیے ڈیٹا (بائٹس) کا ایک بڑا سلسلہ ہوتا ہے۔

GPU کا مطلب ہے گرافکس پروسیسنگ یونٹ۔ مدر بورڈ پر موجود یہ بلاک متن اور متحرک یا ساکن تصاویر کو اسکرین پر بھیجنے کا ذمہ دار ہے۔

جدید کمپیوٹرز (PCs) کے ساتھ، کوئی صرف پڑھنے کی میموری (ROM) نہیں ہے۔ تاہم، BIOS یا UEFI ہے جو کہ ایک قسم کی غیر مستحکم RAM ہے۔ BIOS میں موجود معلومات کو دراصل بیٹری کے ذریعے برقرار رکھا جاتا ہے۔ بیٹری وہی ہے جو دراصل گھڑی کے ٹائمر کو کمپیوٹر کے لیے صحیح وقت اور تاریخ پر برقرار رکھتی ہے۔ UEFI کی ایجاد BIOS کے بعد ہوئی تھی، اور اس نے BIOS کی جگہ لے لی ہے حالانکہ BIOS ابھی بھی جدید پی سی میں کافی متعلقہ ہے۔ ہم بعد میں ان پر مزید بات کریں گے!

جدید پی سی میں، µP اور اندرونی پورٹ سرکٹس (اور میموری) کے درمیان ایڈریس اور ڈیٹا بسیں متوازی بسیں نہیں ہیں۔ وہ سیریل بسیں ہیں جن کو ایک سمت میں ٹرانسمیشن کے لیے دو کنڈکٹرز اور مخالف سمت میں ٹرانسمیشن کے لیے دو کنڈکٹرز کی ضرورت ہوتی ہے۔ اس کا مطلب ہے، مثال کے طور پر، کہ 32 بٹس کو کسی بھی سمت میں سیریز میں (ایک کے بعد ایک بٹ) بھیجا جا سکتا ہے۔

اگر سیریل ٹرانسمیشن دو کنڈکٹرز (دو لائنوں) کے ساتھ صرف ایک سمت میں ہے، تو اسے ہاف ڈوپلیکس کہا جاتا ہے۔ اگر سیریل ٹرانسمیشن دونوں سمتوں میں چار کنڈکٹرز کے ساتھ ہے، دونوں سمتوں میں ایک جوڑا، جسے فل ڈوپلیکس کہا جاتا ہے۔

جدید کمپیوٹر کی پوری میموری اب بھی بائٹ مقامات کی ایک سیریز پر مشتمل ہے: آٹھ بٹس فی بائٹ۔ ایک جدید کمپیوٹر میں میموری کی جگہ کم از کم 4 گیگا بائٹس = 4 x 210 x 2 ہوتی ہے۔ 10 x 2 10 = 4 x 1,073,741,824 10 بائٹس = 4 x 1024 10 x 1024 10 x 1024 10 = 4 x 1,073,741,824 10 .

نوٹ : اگرچہ پچھلے مدر بورڈ پر کوئی ٹائمر سرکٹ نہیں دکھایا گیا ہے، لیکن تمام جدید مدر بورڈز میں ٹائمر سرکٹ ہوتے ہیں۔

6.3 x64 کمپیوٹر آرکیٹیکچر کی بنیادی باتیں

6.31 x64 رجسٹر سیٹ

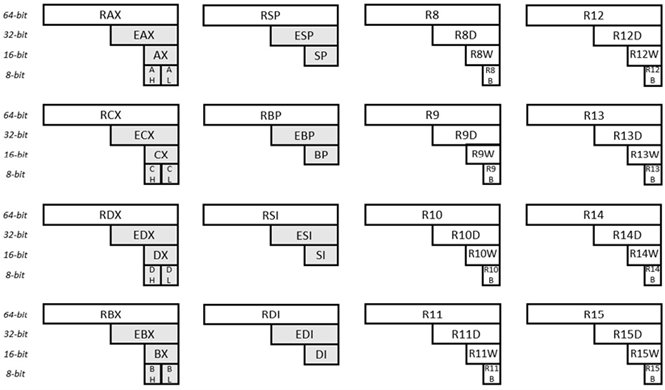

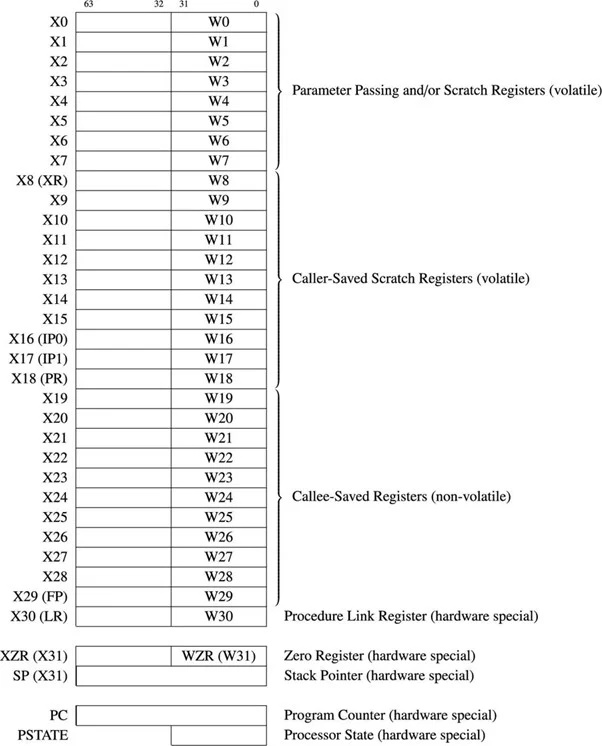

مائیکرو پروسیسرز کی x86 سیریز کا 64 بٹ مائکرو پروسیسر ایک 64 بٹ مائکرو پروسیسر ہے۔ اسی سیریز کے 32 بٹ پروسیسر کو تبدیل کرنا کافی جدید ہے۔ 64 بٹ مائکرو پروسیسر کے عمومی مقصد کے رجسٹر اور ان کے نام درج ذیل ہیں:

تصویر 6.31 x64 کے لیے عام مقصد کے رجسٹر

دی گئی مثال میں سولہ (16) عام مقصد کے رجسٹر دکھائے گئے ہیں۔ ان میں سے ہر ایک رجسٹر 64 بٹ چوڑا ہے۔ اوپر بائیں کونے میں رجسٹر کو دیکھ کر، 64 بٹس کی شناخت RAX کے طور پر ہوتی ہے۔ اسی رجسٹر کے پہلے 32 بٹس (دائیں طرف سے) کی شناخت EAX کے طور پر کی گئی ہے۔ اسی رجسٹر کے پہلے 16 بٹس (دائیں سے) AX کے طور پر شناخت کیے گئے ہیں۔ اسی رجسٹر کے دوسرے بائٹ (دائیں طرف سے) کی شناخت اے ایچ (یہاں ایچ کا مطلب ہے اعلی) کے طور پر کی گئی ہے۔ اور پہلا بائٹ (اسی رجسٹر کا) AL (یہاں L کا مطلب کم ہے) کے طور پر شناخت کیا گیا ہے۔ نیچے دائیں کونے میں رجسٹر کو دیکھ کر، 64 بٹس کی شناخت R15 کے طور پر ہوتی ہے۔ اسی رجسٹر کے پہلے 32 بٹس کی شناخت R15D کے طور پر کی گئی ہے۔ اسی رجسٹر کے پہلے 16 بٹس کی شناخت R15W کے طور پر کی گئی ہے۔ اور پہلے بائٹ کی شناخت R15B کے طور پر کی گئی ہے۔ دوسرے رجسٹروں (اور سب رجسٹروں) کے نام بھی اسی طرح بیان کیے گئے ہیں۔

Intel اور AMD µPs کے درمیان کچھ فرق ہیں۔ اس سیکشن میں معلومات Intel کے لیے ہیں۔

6502 µP کے ساتھ، پروگرام کاؤنٹر رجسٹر (براہ راست قابل رسائی نہیں) جس پر عمل درآمد کی اگلی ہدایات ہوتی ہیں 16 بٹس چوڑا ہے۔ یہاں (x64)، پروگرام کاؤنٹر کو انسٹرکشن پوائنٹر کہا جاتا ہے، اور یہ 64 بٹ چوڑا ہے۔ اسے RIP کا لیبل لگا ہوا ہے۔ اس کا مطلب یہ ہے کہ x64 µP 264 = 1.844674407 x 1019 (اصل میں 18,446,744,073,709,551,616) میموری بائٹ مقامات کو ایڈریس کرسکتا ہے۔ RIP عام مقصد کا رجسٹر نہیں ہے۔

اسٹیک پوائنٹر رجسٹر یا آر ایس پی 16 عام مقصد کے رجسٹروں میں شامل ہے۔ یہ میموری میں آخری اسٹیک اندراج کی طرف اشارہ کرتا ہے۔ 6502 µP کی طرح، x64 کے لیے اسٹیک نیچے کی طرف بڑھتا ہے۔ x64 کے ساتھ، RAM میں اسٹیک کو سب روٹینز کے لیے واپسی کے پتے ذخیرہ کرنے کے لیے استعمال کیا جاتا ہے۔ یہ 'شیڈو اسپیس' کو ذخیرہ کرنے کے لیے بھی استعمال ہوتا ہے (مندرجہ ذیل بحث کو دیکھیں)۔

6502 µP میں 8 بٹ پروسیسر اسٹیٹس رجسٹر ہے۔ x64 میں مساوی کو RFLAGS رجسٹر کہا جاتا ہے۔ یہ رجسٹر ان جھنڈوں کو محفوظ کرتا ہے جو آپریشن کے نتائج اور پروسیسر (µP) کو کنٹرول کرنے کے لیے استعمال ہوتے ہیں۔ یہ 64 بٹ چوڑا ہے۔ اعلی 32 بٹس محفوظ ہیں اور فی الحال استعمال نہیں ہوتے ہیں۔ درج ذیل جدول RFLAGS رجسٹر میں عام طور پر استعمال ہونے والے بٹس کے نام، انڈیکس اور معنی دیتا ہے:

| جدول 6.31.1 سب سے زیادہ استعمال شدہ RFLAGS جھنڈے (بٹس) |

|||

|---|---|---|---|

| علامت | بٹ | نام | مقصد |

| سی ایف | 0 | لے جانا | یہ مقرر کیا جاتا ہے اگر ایک ریاضی کا عمل نتیجہ کے سب سے اہم حصے سے ایک لے یا ادھار پیدا کرتا ہے؛ دوسری صورت میں صاف. یہ جھنڈا غیر دستخط شدہ عددی ریاضی کے لیے اوور فلو حالت کی نشاندہی کرتا ہے۔ یہ ایک سے زیادہ درست ریاضی میں بھی استعمال ہوتا ہے۔ |

| پی ایف | 2 | برابری | یہ سیٹ کیا جاتا ہے اگر نتیجہ کے کم سے کم اہم بائٹ میں 1 بٹس کی برابر تعداد ہو؛ دوسری صورت میں صاف. |

| آف | 4 | ایڈجسٹ کریں۔ | یہ مقرر کیا جاتا ہے اگر ایک ریاضی کا عمل نتیجہ کے بٹ 3 میں سے ایک کیری یا ادھار پیدا کرتا ہے۔ دوسری صورت میں صاف. یہ پرچم بائنری کوڈڈ ڈیسیمل (BCD) ریاضی میں استعمال ہوتا ہے۔ |

| زیڈ ایف | 6 | صفر | یہ سیٹ کیا جاتا ہے اگر نتیجہ صفر ہے؛ دوسری صورت میں صاف. |

| ایس ایف | 7 | دستخط | یہ سیٹ کیا جاتا ہے اگر یہ نتیجہ کے سب سے اہم بٹ کے برابر ہے جو ایک دستخط شدہ عدد کا نشان بٹ ہے (0 ایک مثبت قدر کی نشاندہی کرتا ہے اور 1 منفی قدر کی نشاندہی کرتا ہے)۔ |

| آف | گیارہ | اوور فلو | یہ سیٹ کیا جاتا ہے اگر انٹیجر کا نتیجہ بہت بڑا مثبت نمبر یا بہت چھوٹا منفی نمبر (سائن بٹ کو چھوڑ کر) منزل کے کام میں فٹ ہونے کے لیے؛ دوسری صورت میں صاف. یہ جھنڈا دستخط شدہ عدد (دو کے تکمیلی) ریاضی کے لیے اوور فلو حالت کی نشاندہی کرتا ہے۔ |

| ڈی ایف | 10 | سمت | یہ سیٹ کیا جاتا ہے اگر سمت کے تار کی ہدایات کام کرتی ہیں (اضافہ یا کمی)۔ |

| ID | اکیس | شناخت | یہ سیٹ کیا جاتا ہے اگر اس کی تبدیلی CPUID ہدایات کی موجودگی کی نشاندہی کرتی ہے۔ |

اٹھارہ 64 بٹ رجسٹروں کے علاوہ جو پہلے اشارہ کیا گیا ہے، x64 آرکیٹیکچر µP میں فلوٹنگ پوائنٹ ریاضی کے لیے آٹھ 80 بٹ چوڑے رجسٹر ہیں۔ ان آٹھ رجسٹروں کو MMX رجسٹر کے طور پر بھی استعمال کیا جا سکتا ہے (مندرجہ ذیل بحث کو دیکھیں)۔ XMM کے لیے سولہ 128 بٹ رجسٹر بھی ہیں (مندرجہ ذیل بحث کا حوالہ دیں)۔

یہ سب رجسٹروں کے بارے میں نہیں ہے۔ مزید x64 رجسٹر ہیں جو سیگمنٹ رجسٹر ہیں (زیادہ تر x64 میں غیر استعمال شدہ)، کنٹرول رجسٹر، میموری مینجمنٹ رجسٹر، ڈیبگ رجسٹر، ورچوئلائزیشن رجسٹر، پرفارمنس رجسٹر جو ہر طرح کے اندرونی پیرامیٹرز کو ٹریک کرتے ہیں (کیش ہٹس/مسز، مائیکرو آپس ایگزیکیٹڈ ، اور بہت کچھ).

سمڈ

SIMD کا مطلب ہے سنگل انسٹرکشن ایک سے زیادہ ڈیٹا۔ اس کا مطلب یہ ہے کہ اسمبلی کی ایک زبان کی ہدایات ایک مائکرو پروسیسر میں ایک ہی وقت میں متعدد ڈیٹا پر کام کر سکتی ہیں۔ مندرجہ ذیل جدول پر غور کریں:

| 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | |

| + | 9 | 10 | گیارہ | 12 | 13 | 14 | پندرہ | 16 |

| = | 10 | 12 | 14 | 16 | 18 | بیس | 22 | 24 |

اس جدول میں، آٹھ جوابات دینے کے لیے نمبروں کے آٹھ جوڑے متوازی (اسی دورانیے میں) شامل کیے گئے ہیں۔ اسمبلی کی ایک زبان کی ہدایت MMX رجسٹروں میں آٹھ متوازی عددی اضافے کر سکتی ہے۔ اسی طرح کا کام XMM رجسٹروں کے ساتھ کیا جا سکتا ہے۔ لہذا، عدد کے لیے MMX ہدایات اور فلوٹس کے لیے XMM ہدایات ہیں۔

6.32 میموری کا نقشہ اور x64

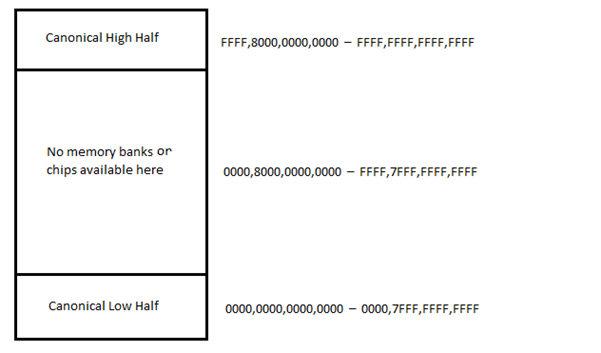

انسٹرکشن پوائنٹر (پروگرام کاؤنٹر) کے 64 بٹس کے ساتھ، اس کا مطلب ہے کہ 264 = 1.844674407 x 1019 میموری بائٹ لوکیشنز کو ایڈریس کیا جا سکتا ہے۔ ہیکساڈیسیمل میں، سب سے زیادہ بائٹ لوکیشن FFFF، FFFF، FFFF، FFFF16 ہے۔ آج کا کوئی عام کمپیوٹر اتنی بڑی میموری (مکمل) جگہ فراہم نہیں کر سکتا۔ لہذا، x64 کمپیوٹر کے لیے ایک مناسب میموری نقشہ درج ذیل ہے:

دھیان دیں کہ 0000,8000,0000,000016 سے FFFF,7FFF,FFFF,FFFF16 تک کے فرق میں میموری کی کوئی جگہ نہیں ہے (کوئی میموری ریم بینک نہیں ہے)۔ یہ FFFF,0000,0000,000116 کا فرق ہے جو کافی بڑا ہے۔ کینونیکل ہائی ہاف میں آپریٹنگ سسٹم ہوتا ہے، جبکہ کینونیکل لو ہاف میں صارف کے پروگرام (ایپلی کیشنز) اور ڈیٹا ہوتا ہے۔ آپریٹنگ سسٹم دو حصوں پر مشتمل ہے: ایک چھوٹا UEFI (BIOS) اور ایک بڑا حصہ جو ہارڈ ڈرائیو سے لوڈ ہوتا ہے۔ اگلا باب جدید آپریٹنگ سسٹمز کے بارے میں مزید بات کرتا ہے۔ اس میموری میپ اور کموڈور-64 کے ساتھ مماثلت کو نوٹ کریں جب 64KB بہت زیادہ میموری کی طرح نظر آتا تھا۔

اس تناظر میں، آپریٹنگ سسٹم کو تقریباً 'کرنل' کہا جاتا ہے۔ دانا کموڈور-64 کمپیوٹر کے کرنل سے ملتا جلتا ہے، لیکن اس میں کہیں زیادہ سب روٹینز ہیں۔

x64 کے لیے endianness تھوڑا endian ہے، جس کا مطلب ہے کہ کسی مقام کے لیے، نچلا ایڈریس میموری میں موجود نچلے مواد کی بائٹ کی طرف اشارہ کرتا ہے۔

x64 کے لیے 6.33 اسمبلی لینگویج ایڈریسنگ موڈز

ایڈریسنگ موڈز وہ طریقے ہیں جن سے ایک ہدایت µP رجسٹر اور میموری تک رسائی حاصل کر سکتی ہے (بشمول اندرونی پورٹ رجسٹر)۔ x64 میں ایڈریسنگ کے بہت سے طریقے ہیں، لیکن یہاں صرف عام طور پر استعمال ہونے والے ایڈریسنگ موڈز کو ایڈریس کیا گیا ہے۔ یہاں ایک ہدایت کے لئے عام نحو ہے:

opcode منزل، ذریعہ

اعشاریہ نمبر بغیر کسی سابقہ یا لاحقہ کے لکھے جاتے ہیں۔ 6502 کے ساتھ، ماخذ مضمر ہے۔ x64 میں 6502 کے مقابلے میں زیادہ اوپ کوڈز ہیں، لیکن کچھ اوپکوڈز میں ایک جیسی یادداشتیں ہیں۔ انفرادی x64 ہدایات متغیر لمبائی کی ہیں اور سائز میں 1 سے 15 بائٹس تک ہوسکتی ہیں۔ عام طور پر استعمال ہونے والے ایڈریسنگ موڈز مندرجہ ذیل ہیں:

فوری ایڈریسنگ موڈ

یہاں، سورس آپرینڈ ایک اصل قدر ہے نہ کہ پتہ یا لیبل۔ مثال (تبصرہ پڑھیں):

EAX شامل کریں، 14؛ 64 بٹ RAX کے اعشاریہ 14 سے 32 بٹ EAX شامل کریں، جواب EAX (منزل) میں باقی ہے

ایڈریسنگ موڈ کو رجسٹر کرنے کے لیے رجسٹر کریں۔

مثال:

شامل کریں R8B, AL ; RAX کے 8 بٹ AL کو 64 بٹ R8 کے R8B میں شامل کریں - جوابات R8B میں باقی ہیں (منزل)

بالواسطہ اور انڈیکسڈ ایڈریسنگ موڈ

6502 µP کے ساتھ بالواسطہ ایڈریس کا مطلب ہے کہ ہدایات میں دیے گئے پتے کے مقام پر حتمی مقام کا موثر پتہ (پوائنٹر) ہے۔ ایکس 64 کے ساتھ بھی ایسا ہی ہوتا ہے۔ 6502 µP کے ساتھ انڈیکس ایڈریسنگ کا مطلب یہ ہے کہ µP رجسٹر کا مواد موثر ایڈریس رکھنے کے لیے ہدایات میں دیے گئے پتے میں شامل کیا جاتا ہے۔ ایکس 64 کے ساتھ بھی ایسا ہی ہوتا ہے۔ نیز، x64 کے ساتھ، دیے گئے پتے پر شامل کیے جانے سے پہلے رجسٹر کے مواد کو 1 یا 2 یا 4 یا 8 سے بھی ضرب دیا جا سکتا ہے۔ x64 کی mov (کاپی) ہدایات بالواسطہ اور اشاریہ شدہ ایڈریسنگ دونوں کو یکجا کرسکتی ہیں۔ مثال:

MOV R8W, 1234[8*RAX+RCX] ; ایڈریس پر لفظ منتقل کریں (8 x RAX + RCX) + 1234

یہاں، R8W کے پاس R8 کے پہلے 16 بٹس ہیں۔ دیا گیا پتہ 1234 ہے۔ RAX رجسٹر میں ایک 64 بٹ نمبر ہے جسے 8 سے ضرب دیا جاتا ہے۔ نتیجہ 64 بٹ RCX رجسٹر کے مواد میں شامل کیا جاتا ہے۔ یہ دوسرا نتیجہ موثر ایڈریس حاصل کرنے کے لیے دیے گئے پتے میں شامل کیا جاتا ہے جو 1234 ہے۔ مؤثر ایڈریس کے مقام پر موجود نمبر کو R8 رجسٹر کے پہلے 16 بٹ جگہ (R8W) پر منتقل کیا جاتا ہے، جو کچھ بھی تھا اسے تبدیل کر دیا جاتا ہے۔ مربع بریکٹ کے استعمال پر توجہ دیں۔ یاد رکھیں کہ x64 میں ایک لفظ 16 بٹ چوڑا ہے۔

RIP رشتہ دار خطاب

6502 µP کے لیے، متعلقہ ایڈریسنگ صرف برانچ ہدایات کے ساتھ استعمال ہوتی ہے۔ وہاں، اوپکوڈ کا واحد آپرینڈ ایک آفسیٹ ہے جو مؤثر ہدایات ایڈریس (ڈیٹا ایڈریس نہیں) کے لیے پروگرام کاؤنٹر کے مواد میں شامل یا گھٹایا جاتا ہے۔ ایکس 64 کے ساتھ بھی ایسا ہی ہوتا ہے جہاں پروگرام کاؤنٹر کو انسٹرکشن پوائنٹر کہا جاتا ہے۔ x64 کے ساتھ ہدایات صرف برانچ کی ہدایات نہیں ہوتی ہیں۔ RIP- متعلق ایڈریسنگ کی ایک مثال یہ ہے:

MOV AL، [RIP]

RAX کے AL میں 8 بٹ پر دستخط شدہ نمبر ہے جو اگلی ہدایات کی طرف اشارہ کرنے کے لیے RIP (64-bit انسٹرکشن پوائنٹر) میں موجود مواد سے شامل یا گھٹایا جاتا ہے۔ نوٹ کریں کہ اس ہدایت میں ماخذ اور منزل کو غیر معمولی طور پر تبدیل کیا گیا ہے۔ مربع بریکٹ کے استعمال کو بھی نوٹ کریں جو RIP کے مواد کا حوالہ دیتے ہیں۔

6.34 x64 کی عام استعمال شدہ ہدایات

درج ذیل جدول میں * کا مطلب ہے opcodes کے ذیلی سیٹ کے مختلف ممکنہ لاحقے:

| جدول 6.34.1 x64 میں عام طور پر استعمال ہونے والی ہدایات |

|

|---|---|

| اوپکوڈ | مطلب |

| MOV | میموری اور رجسٹروں کے درمیان/سے/میں (کاپی) منتقل کریں۔ |

| CMOV* | مختلف مشروط حرکتیں۔ |

| ایکس سی ایچ جی | تبادلہ |

| بی ایس ڈبلیو اے پی | بائٹ سویپ |

| پش/پاپ | اسٹیک کا استعمال |

| ADD/ADC | کیری کے ساتھ شامل کریں۔ |

| SUB/SBC | گھٹائیں/کیری کے ساتھ |

| MUL/IMUL | ضرب/غیر دستخط شدہ |

| DIV/IDIV | تقسیم/غیر دستخط شدہ |

| INC/DEC | اضافہ/کمی |

| این ای جی | نفی کرنا |

| سی ایم پی | موازنہ کریں۔ |

| اور/یا/XOR/نہیں | بٹ وائز آپریشنز |

| SHR/SAR | دائیں منطقی/ریاضی کو شفٹ کریں۔ |

| SHL/SAL | منطقی/ریاضی کو بائیں منتقل کریں۔ |

| ROR/ROLE | دائیں/بائیں گھمائیں۔ |

| RCR/RCL | کیری بٹ کے ذریعے دائیں/بائیں گھمائیں۔ |

| BT/BTS/BTR | بٹ ٹیسٹ/اور سیٹ/اور ری سیٹ |

| جے ایم پی | غیر مشروط چھلانگ |

| JE/JNE/JC/JNC/J* | چھلانگ لگائیں اگر مساوی/برابر نہ ہو/کیری نہ ہو/نہ لے جائے/کئی دیگر |

| واک / واک / واک | ECX کے ساتھ لوپ |

| کال/RET | سب روٹین/واپس کال کریں۔ |

| NOP | کوئی آپریشن نہیں۔ |

| سی پی یو آئی ڈی | سی پی یو کی معلومات |

x64 میں ضرب اور تقسیم کی ہدایات ہیں۔ اس کے µP میں ضرب اور تقسیم ہارڈویئر سرکٹس ہیں۔ 6502 µP میں ضرب اور تقسیم ہارڈویئر سرکٹس نہیں ہیں۔ ہارڈ ویئر کے ذریعے ضرب اور تقسیم کرنا سافٹ ویئر کے ذریعے تیز تر ہے (بشمول بٹس کی شفٹنگ)۔

سٹرنگ ہدایات

اسٹرنگ کی بہت سی ہدایات ہیں، لیکن یہاں صرف ایک ہی بات کی جائے گی جس پر MOVS (موو سٹرنگ کے لیے) ایڈریس C000 سے شروع ہونے والی اسٹرنگ کو کاپی کرنے کی ہدایت ہے۔ ایچ . ایڈریس C100 پر شروع کرنے کے لیے ایچ مندرجہ ذیل ہدایات کا استعمال کریں:

MOVS [C100H], [C000H]

ہیکساڈیسیمل کے لیے H لاحقہ نوٹ کریں۔

6.35 x64 میں لوپنگ

6502 µP میں لوپنگ کے لیے برانچ کی ہدایات ہیں۔ ایک برانچ انسٹرکشن چھلانگ لگا کر ایڈریس کے مقام پر پہنچ جاتی ہے جس میں نئی ہدایات ہوتی ہیں۔ پتہ کی جگہ کو 'لوپ' کہا جا سکتا ہے۔ x64 میں لوپنگ کے لیے LOOP/LOOPE/LOOPNE ہدایات ہیں۔ اسمبلی زبان کے ان مخصوص الفاظ کو 'لوپ' لیبل (بغیر اقتباسات کے) کے ساتھ الجھایا نہیں جانا چاہیے۔ طرز عمل مندرجہ ذیل ہے:

LOOP ECX کو کم کرتا ہے اور چیک کرتا ہے کہ آیا ECX صفر نہیں ہے۔ اگر وہ شرط (صفر) پوری ہو جاتی ہے، تو یہ ایک مخصوص لیبل پر چھلانگ لگا دیتا ہے۔ بصورت دیگر، یہ گزر جائے گا (مندرجہ ذیل بحث میں باقی ہدایات کے ساتھ جاری رکھیں)۔

LOOPE ECX کو کم کرتا ہے اور چیک کرتا ہے کہ ECX صفر نہیں ہے (مثال کے طور پر 1 ہو سکتا ہے) اور ZF سیٹ ہے (1 پر)۔ اگر یہ شرائط پوری ہوجاتی ہیں، تو یہ لیبل پر چھلانگ لگا دیتا ہے۔ دوسری صورت میں، یہ گر جاتا ہے.

LOOPNE ECX کو کم کرتا ہے اور چیک کرتا ہے کہ ECX صفر نہیں ہے اور ZF سیٹ نہیں ہے (یعنی صفر ہو)۔ اگر یہ شرائط پوری ہوجاتی ہیں، تو یہ لیبل پر چھلانگ لگا دیتا ہے۔ دوسری صورت میں، یہ گر جاتا ہے.

x64 کے ساتھ، RCX رجسٹر یا اس کے ذیلی حصے جیسے ECX یا CX، کاؤنٹر انٹیجر رکھتا ہے۔ LOOP ہدایات کے ساتھ، کاؤنٹر عام طور پر گنتی کرتا ہے، ہر چھلانگ (لوپ) کے لیے 1 کی کمی کرتا ہے۔ مندرجہ ذیل لوپنگ کوڈ سیگمنٹ میں، EAX رجسٹر میں نمبر دس تکرار میں 0 سے 10 تک بڑھ جاتا ہے جبکہ ECX میں نمبر 10 گنا کم ہوتا ہے (تبصرے پڑھیں):

MOV EAX، 0 ;

MOV ECX، 10؛ پہلے سے طے شدہ طور پر 10 بار گنتی کریں، ہر تکرار کے لیے ایک بار

لیبل:

INC EAX ; لوپ باڈی کے طور پر EAX میں اضافہ کریں۔

لوپ لیبل؛ EAX کو کم کریں، اور اگر EAX صفر نہیں ہے، تو 'لیبل:' سے لوپ باڈی کو دوبارہ چلائیں۔

لوپ کوڈنگ 'لیبل:' سے شروع ہوتی ہے۔ بڑی آنت کے استعمال کو نوٹ کریں۔ لوپ کوڈنگ 'LOOP لیبل' کے ساتھ ختم ہوتی ہے جو کہ decrement EAX کہتا ہے۔ اگر اس کا مواد صفر نہیں ہے، تو 'لیبل:' کے بعد ہدایات پر واپس جائیں اور 'LOOP لیبل' تک نیچے کی طرف آنے والی کسی بھی ہدایات (باڈی کی تمام ہدایات) پر دوبارہ عمل کریں۔ نوٹ کریں کہ 'لیبل' کا اب بھی دوسرا نام ہو سکتا ہے۔

x64 کا 6.36 ان پٹ/آؤٹ پٹ

باب کا یہ حصہ ڈیٹا کو آؤٹ پٹ (اندرونی) بندرگاہ پر بھیجنے یا ان پٹ (اندرونی) بندرگاہ سے ڈیٹا وصول کرنے سے متعلق ہے۔ چپ سیٹ میں آٹھ بٹ پورٹس ہیں۔ کوئی بھی دو لگاتار 8 بٹ بندرگاہوں کو 16 بٹ پورٹ سمجھا جا سکتا ہے، اور کوئی بھی چار لگاتار بندرگاہیں 32 بٹ پورٹ ہو سکتی ہیں۔ اس طریقے سے، پروسیسر 8، 16، یا 32 بٹس کو کسی بیرونی ڈیوائس میں یا اس سے منتقل کر سکتا ہے۔

معلومات کو پروسیسر اور اندرونی بندرگاہ کے درمیان دو طریقوں سے منتقل کیا جا سکتا ہے: اسے استعمال کرتے ہوئے جسے میموری میپڈ ان پٹ/آؤٹ پٹ کہا جاتا ہے یا علیحدہ ان پٹ/آؤٹ پٹ ایڈریس اسپیس کا استعمال۔ میموری میپڈ I/O ایسا ہی ہے جو 6502 پروسیسر کے ساتھ ہوتا ہے جہاں پورٹ ایڈریس دراصل میموری کی پوری جگہ کا حصہ ہوتے ہیں۔ اس صورت میں، ڈیٹا کو کسی خاص ایڈریس والے مقام پر بھیجتے وقت، یہ میموری بینک میں نہیں بلکہ بندرگاہ پر جاتا ہے۔ بندرگاہوں میں علیحدہ I/O ایڈریس کی جگہ ہوسکتی ہے۔ اس مؤخر الذکر صورت میں، تمام میموری بینکوں کے پاس ان کے پتے صفر سے ہوتے ہیں۔ 0000H سے FFFF16 تک ایک الگ ایڈریس رینج ہے۔ یہ چپ سیٹ میں بندرگاہوں کے ذریعہ استعمال ہوتے ہیں۔ مدر بورڈ کو اس لیے پروگرام کیا گیا ہے کہ میموری میپ شدہ I/O اور علیحدہ I/O ایڈریس اسپیس کے درمیان الجھن نہ ہو۔

میموری میپڈ I/O

اس کے ساتھ، بندرگاہوں کو میموری کے مقامات کے طور پر سمجھا جاتا ہے، اور میموری اور µP کے درمیان استعمال ہونے والے عام آپکوڈز کو µP اور بندرگاہوں کے درمیان ڈیٹا کی منتقلی کے لیے استعمال کیا جاتا ہے۔ لہذا، ایڈریس F000H پر موجود پورٹ سے بائٹ کو µP رجسٹر RAX:EAX:AX:AL پر منتقل کرنے کے لیے، درج ذیل کریں:

MOV AL, [F000H]

ایک تار کو میموری سے بندرگاہ میں منتقل کیا جاسکتا ہے اور اس کے برعکس۔ مثال:

MOVS [F000H], [C000H] ; ماخذ C000H ہے، اور منزل F000H پر بندرگاہ ہے۔

I/O ایڈریس کی جگہ الگ کریں۔

اس کے ساتھ ان پٹ اور آؤٹ پٹ کے لیے خصوصی ہدایات کا استعمال کرنا ہوگا۔

سنگل آئٹمز کی منتقلی

منتقلی کے لیے پروسیسر رجسٹر RAX ہے۔ دراصل، یہ ہے RAX:EAX ڈبل ورڈ کے لیے، RAX:EAX:AX لفظ کے لیے، اور RAX:EAX:AX:AL بائٹ کے لیے۔ لہذا، FFF0h پر پورٹ سے بائٹ کو RAX:EAX:AX:AL پر منتقل کرنے کے لیے، درج ذیل ٹائپ کریں:

IN AL, [FFF0H]

ریورس ٹرانسفر کے لیے، درج ذیل کو ٹائپ کریں:

باہر [FFF0H]، AL

لہذا، واحد آئٹمز کے لیے، ہدایات اندر اور باہر ہیں۔ پورٹ ایڈریس RDX:EDX:DX رجسٹر میں بھی دیا جا سکتا ہے۔

ٹرانسفرنگ سٹرنگز

اسٹرنگ کو میموری سے چپ سیٹ پورٹ میں منتقل کیا جا سکتا ہے اور اس کے برعکس۔ FFF0H ایڈریس پر موجود بندرگاہ سے سٹرنگ کو میموری میں منتقل کرنے کے لیے، C100H سے شروع کریں، ٹائپ کریں:

INS [ESI]، [DX]

جس کا ایک ہی اثر ہے جیسے:

INS [EDI]، [DX]

پروگرامر کو FFF0H کا دو بائٹ پورٹ ایڈریس RDX:EDX:Dx رجسٹر میں ڈالنا چاہیے، اور C100H کا دو بائٹ ایڈریس RSI:ESI یا RDI:EDI رجسٹر میں ڈالنا چاہیے۔ ریورس ٹرانسفر کے لیے، درج ذیل کریں:

INS [DX]، [ESI]

جس کا ایک ہی اثر ہے جیسے:

INS [DX]، [EDI]

6.37 x64 میں اسٹیک

6502 پروسیسر کی طرح، x64 پروسیسر میں بھی RAM میں اسٹیک ہوتا ہے۔ x64 کے لیے اسٹیک 2 ہو سکتا ہے۔ 16 = 65,536 بائٹس لمبا یا یہ 2 ہوسکتا ہے۔ 32 = 4,294,967,296 بائٹس لمبا۔ یہ نیچے کی طرف بھی بڑھتا ہے۔ جب رجسٹر کے مواد کو اسٹیک پر دھکیل دیا جاتا ہے، تو RSP اسٹیک پوائنٹر میں نمبر 8 تک کم ہوجاتا ہے۔ یاد رکھیں کہ x64 کے لیے میموری ایڈریس 64 بٹس چوڑا ہے۔ µP میں اسٹیک پوائنٹر کی قدر RAM میں اسٹیک میں اگلے مقام کی طرف اشارہ کرتی ہے۔ جب رجسٹر کا مواد (یا ایک آپرینڈ میں ایک قدر) کو اسٹیک سے رجسٹر میں پاپ کیا جاتا ہے، تو RSP اسٹیک پوائنٹر میں نمبر 8 تک بڑھ جاتا ہے۔ آپریٹنگ سسٹم اسٹیک کے سائز اور RAM میں کہاں سے شروع ہوتا ہے اس کا فیصلہ کرتا ہے۔ اور نیچے کی طرف بڑھتا ہے. یاد رکھیں کہ اسٹیک ایک Last-In-First-Out (LIFO) ڈھانچہ ہے جو نیچے کی طرف بڑھتا ہے اور اس صورت میں اوپر کی طرف سکڑتا ہے۔

µP RBX رجسٹر کے مواد کو اسٹیک پر دھکیلنے کے لیے، درج ذیل کام کریں:

RBX کو پش کریں۔

اسٹیک میں آخری اندراج کو RBX پر واپس کرنے کے لیے، درج ذیل کام کریں:

POP RBX

6.38 x64 میں طریقہ کار

x64 میں سب روٹین کو 'طریقہ کار' کہا جاتا ہے۔ اسٹیک یہاں 6502 µP کے استعمال سے زیادہ استعمال ہوتا ہے۔ ایک x64 طریقہ کار کے لیے نحو ہے:

proc_name:

طریقہ کار جسم

…

صحیح

جاری رکھنے سے پہلے، نوٹ کریں کہ x64 سب روٹین (عام طور پر اسمبلی کی زبان کی ہدایات) کے لیے اوپکوڈز اور لیبلز غیر حساس ہیں۔ یہ proc_name ہے PROC_NAME جیسا ہی ہے۔ 6502 کی طرح، طریقہ کار کے نام (لیبل) کا نام اسمبلی لینگویج کے ٹیکسٹ ایڈیٹر میں ایک نئی لائن کے شروع میں شروع ہوتا ہے۔ اس کے بعد بڑی آنت آتی ہے نہ کہ 6502 کی طرح اسپیس اور اوپ کوڈ کے ذریعے۔ سبروٹین باڈی اس کے بعد آتی ہے، جس کا اختتام RET پر ہوتا ہے نہ کہ RTS کے ساتھ جیسا کہ 6502 µP ہوتا ہے۔ 6502 کی طرح، جسم میں ہر ہدایت، بشمول RET، اپنی لائن کے آغاز سے شروع نہیں ہوتی۔ نوٹ کریں کہ یہاں ایک لیبل 8 حروف سے زیادہ لمبا ہو سکتا ہے۔ اس طریقہ کار کو کال کرنے کے لیے، ٹائپ کردہ طریقہ کار کے اوپر یا نیچے سے، درج ذیل کریں:

proc_name کو کال کریں۔

6502 کے ساتھ، لیبل کا نام صرف کال کرنے کے لیے ٹائپ ہے۔ تاہم، یہاں، مخصوص لفظ 'CALL' یا 'call' ٹائپ کیا جاتا ہے، اس کے بعد اسپیس کے بعد طریقہ کار (subroutine) کا نام آتا ہے۔

طریقہ کار سے نمٹنے کے دوران، عام طور پر دو طریقہ کار ہوتے ہیں۔ ایک طریقہ کار دوسرے کو کال کرتا ہے۔ وہ طریقہ کار جو کال کرتا ہے (جس میں کال کی ہدایت ہوتی ہے) اسے 'کالر' کہا جاتا ہے، اور جس طریقہ کار کو کال کیا جاتا ہے اسے 'کالی' کہا جاتا ہے۔ پیروی کرنے کے لئے ایک کنونشن (قواعد) ہے۔

کال کرنے والے کے اصول

سب روٹین کی درخواست کرتے وقت کال کرنے والے کو درج ذیل اصولوں پر عمل کرنا چاہیے:

1. سب روٹین کو کال کرنے سے پہلے، کال کرنے والے کو کچھ رجسٹروں کے مواد کو محفوظ کرنا چاہیے جنہیں اسٹیک کرنے کے لیے کالر کے ذریعے محفوظ کیا گیا ہے۔ کالر کے ذریعے محفوظ کیے گئے رجسٹر R10, R11، اور کوئی بھی رجسٹر جس میں پیرامیٹرز رکھے گئے ہیں (RDI, RSI, RDX, RCX, R8, R9)۔ اگر ان رجسٹروں کے مواد کو سب روٹین کال میں محفوظ کرنا ہے، تو انہیں RAM میں محفوظ کرنے کے بجائے اسٹیک پر دھکیلیں۔ یہ کرنا پڑتا ہے کیونکہ رجسٹروں کو کالی کے ذریعہ پچھلے مواد کو مٹانے کے لئے استعمال کرنا پڑتا ہے۔

2. اگر طریقہ کار مثال کے طور پر دو نمبروں کو شامل کرنا ہے، تو دو نمبر وہ پیرامیٹرز ہیں جنہیں اسٹیک میں منتقل کیا جانا ہے۔ پیرامیٹرز کو سب روٹین میں منتقل کرنے کے لیے، ان میں سے چھ کو درج ذیل رجسٹروں میں ترتیب سے رکھیں: RDI، RSI، RDX، RCX، R8، R9۔ اگر سب روٹین میں چھ سے زیادہ پیرامیٹرز ہیں، تو باقی کو اسٹیک پر الٹ ترتیب میں دھکیل دیں (یعنی آخری پیرامیٹر پہلے)۔ چونکہ اسٹیک نیچے بڑھتا ہے، اضافی پیرامیٹرز میں سے پہلا (واقعی ساتواں پیرامیٹر) سب سے کم پتے پر محفوظ کیا جاتا ہے (پیرامیٹرز کا یہ الٹا تاریخی طور پر فنکشنز (سبروٹائنز) کو پیرامیٹرز کی متغیر تعداد کے ساتھ پاس کرنے کے لیے استعمال کیا جاتا تھا)۔

3. سب روٹین (طریقہ کار) کو کال کرنے کے لیے، کال کی ہدایات استعمال کریں۔ یہ ہدایت واپسی کا پتہ اسٹیک پر پیرامیٹرز کے اوپر (سب سے کم پوزیشن) اور شاخوں کو سب روٹین کوڈ پر رکھتی ہے۔

4. سب روٹین کی واپسی کے بعد (یعنی کال کی ہدایات کے فوراً بعد)، کال کرنے والے کو اسٹیک سے کوئی بھی اضافی پیرامیٹرز (چھ کے علاوہ جو رجسٹر میں محفوظ ہیں) کو ہٹا دینا چاہیے۔ یہ کال کرنے سے پہلے اسٹیک کو اس کی حالت میں بحال کرتا ہے۔

5. کال کرنے والا RAX رجسٹر میں سب روٹین کی واپسی کی قیمت (پتہ) تلاش کرنے کی توقع کر سکتا ہے۔

6. کال کرنے والا کالر کے محفوظ کردہ رجسٹروں (R10, R11، اور پیرامیٹر پاسنگ رجسٹروں میں سے کوئی بھی) مواد کو اسٹیک سے باہر نکال کر بحال کرتا ہے۔ کال کرنے والا فرض کر سکتا ہے کہ سب روٹین کے ذریعہ کسی دوسرے رجسٹر میں ترمیم نہیں کی گئی تھی۔

جس طرح سے کالنگ کنونشن کو تشکیل دیا گیا ہے، عام طور پر ایسا ہوتا ہے کہ ان اقدامات میں سے کچھ (یا زیادہ تر) اسٹیک میں کوئی تبدیلی نہیں کریں گے۔ مثال کے طور پر، اگر چھ یا اس سے کم پیرامیٹرز ہیں، تو اس مرحلے میں اسٹیک پر کچھ بھی نہیں دھکیلا جاتا ہے۔ اسی طرح، پروگرامرز (اور مرتب کرنے والے) عام طور پر ان نتائج کو رکھتے ہیں جن کی وہ پرواہ کرتے ہیں کہ وہ کال کرنے والے کے محفوظ کردہ رجسٹروں سے باہر قدم 1 اور 6 میں اضافی دھکے اور پاپ کو روکتے ہیں۔

پیرامیٹرز کو سب روٹین میں منتقل کرنے کے دو اور طریقے ہیں، لیکن اس آن لائن کیریئر کورس میں ان پر توجہ نہیں دی جائے گی۔ ان میں سے ایک عام مقصد کے رجسٹروں کے بجائے خود اسٹیک کا استعمال کرتا ہے۔

کیلی کے قواعد

سبروٹین کہلانے والی تعریف کو درج ذیل اصولوں پر عمل کرنا چاہیے:

1. رجسٹروں کا استعمال کرتے ہوئے یا اسٹیک پر جگہ بناتے ہوئے مقامی متغیرات (متغیرات جو طریقہ کار کے اندر تیار ہوتے ہیں) مختص کریں۔ یاد رکھیں کہ اسٹیک نیچے کی طرف بڑھتا ہے۔ لہذا، اسٹیک کے اوپر جگہ بنانے کے لیے، اسٹیک پوائنٹر کو کم کیا جانا چاہیے۔ اسٹیک پوائنٹر کو کم کرنے کی مقدار مقامی متغیرات کی مطلوبہ تعداد پر منحصر ہے۔ مثال کے طور پر، اگر ایک مقامی فلوٹ اور ایک مقامی لمبا (کل 12 بائٹس) درکار ہے، تو ان مقامی متغیرات کے لیے جگہ بنانے کے لیے اسٹیک پوائنٹر کو 12 تک کم کرنے کی ضرورت ہے۔ C جیسی اعلیٰ سطح کی زبان میں، اس کا مطلب ہے کہ اقدار کو تفویض کیے بغیر (شروع کیے) متغیرات کا اعلان کرنا۔

2. اس کے بعد، کسی بھی رجسٹر کی ویلیوز جو کہ نامزد کالی محفوظ شدہ ہیں (عام مقصد کے رجسٹر جو کال کرنے والے کے ذریعہ محفوظ نہیں کیے جاتے ہیں) جو فنکشن کے ذریعہ استعمال کیے جاتے ہیں۔ رجسٹروں کو بچانے کے لیے، انہیں اسٹیک پر دھکیلیں۔ کالی محفوظ شدہ رجسٹرز RBX، RBP، اور R12 سے R15 ہیں (RSP بھی کال کنونشن کے ذریعہ محفوظ ہے، لیکن اس مرحلے کے دوران اسٹیک پر دھکیلنے کی ضرورت نہیں ہے)۔

ان تینوں اعمال کو انجام دینے کے بعد، سب روٹین کا اصل عمل آگے بڑھ سکتا ہے۔ جب سب روٹین واپس آنے کے لیے تیار ہو جائے تو کال کنونشن کے قوانین جاری رہتے ہیں۔

3. جب سب روٹین مکمل ہو جائے، تو سب روٹین کی واپسی کی قیمت RAX میں رکھی جائے اگر یہ پہلے سے موجود نہیں ہے۔

4. سب روٹین کو کالی کے محفوظ کردہ رجسٹروں (RBX، RBP، اور R12 سے R15) کی پرانی اقدار کو بحال کرنا چاہیے جن میں ترمیم کی گئی تھی۔ رجسٹر کے مواد کو اسٹیک سے پاپ کرکے بحال کیا جاتا ہے۔ نوٹ کریں کہ رجسٹروں کو الٹا ترتیب میں پاپ کیا جانا چاہئے کہ انہیں دھکیل دیا گیا تھا۔

5. اگلا، ہم مقامی متغیرات کو ڈی ایلوکیٹ کرتے ہیں۔ ایسا کرنے کا سب سے آسان طریقہ یہ ہے کہ RSP میں وہی رقم شامل کی جائے جو اس سے مرحلہ 1 میں منہا کی گئی تھی۔

6. آخر میں، ہم دوبارہ ہدایت پر عمل کرتے ہوئے کال کرنے والے کے پاس واپس آتے ہیں۔ یہ ہدایت اسٹیک سے مناسب واپسی کا پتہ تلاش کرے گی اور اسے ہٹا دے گی۔

دوسرے سب روٹین کو کال کرنے کے لیے کالر سبروٹین کے جسم کی ایک مثال جو کہ 'myFunc' ہے درج ذیل ہے (تبصرے پڑھیں):

; ایک فنکشن 'myFunc' کو کال کرنا چاہتے ہیں جس میں تین لگتے ہیں۔

; عددی پیرامیٹر پہلا پیرامیٹر RAX میں ہے۔

; دوسرا پیرامیٹر مستقل 456 ہے۔ تیسرا

; پیرامیٹر میموری مقام 'متغیر' میں ہے

دھکا rdi ; rdi ایک param ہو گا، لہذا اسے محفوظ کرنا

; long retVal = myFunc ( x , 456 , z ) ;

mov rdi , rax ; RDI میں پہلا پیرامیٹر ڈالیں۔

mov rsi, 456 ; RSI میں دوسرا پیرامیٹر ڈالیں۔

mov rdx , [متغیر] ؛ RDX میں تیسرا پیرامیٹر ڈالیں۔

myFunc کو کال کریں؛ فنکشن کو کال کریں۔

پاپ آر ڈی آئی ؛ محفوظ شدہ RDI قدر کو بحال کریں۔

; myFunc کی واپسی کی قیمت اب RAX میں دستیاب ہے۔

کالی فنکشن (myFunc) کی ایک مثال یہ ہے (تبصرے پڑھیں):

myFunc:

; ∗∗∗ سٹینڈرڈ سب روٹین پرولوگ ∗∗∗

ذیلی آر ایس پی، 8؛ 'sub' opcode کا استعمال کرتے ہوئے 64−bit مقامی متغیر (نتیجہ) کے لیے کمرہ

Rbx کو دھکا؛ کالی محفوظ کریں - رجسٹروں کو محفوظ کریں۔

دھکا rbp؛ دونوں کو myFunc استعمال کرے گا۔

; ∗∗∗ سب روٹین باڈی ∗∗∗

mov rax , rdi ; پیرامیٹر 1 سے RAX تک

mov rbp , rsi ; پیرامیٹر 2 سے RBP

mov rbx , rdx ; پیرامیٹر 3 سے آر بی ایکس

mov [ rsp + 1 6 ] , rbx ; rbx کو مقامی متغیر میں ڈالیں۔

شامل کریں [ rsp + 1 6 ] , rbp ; مقامی متغیر میں rbp شامل کریں۔

mov rax , [rsp +16] ; RAX میں مقامی متغیر کے mov مواد

; (واپسی قدر/حتمی نتیجہ)

; ∗∗∗ معیاری ذیلی روٹین ایپیلاگ ∗∗∗

پاپ آر بی پی ؛ کالی محفوظ رجسٹروں کو بازیافت کریں۔

پاپ آر بی ایکس ؛ جب دھکیل دیا جائے تو الٹ

آر ایس پی شامل کریں، 8؛ ڈیلوکیٹ مقامی متغیر (ے)۔ 8 کا مطلب ہے 8 بائٹس

ret اسٹیک سے پاپ ٹاپ ویلیو، وہاں چھلانگ لگائیں۔

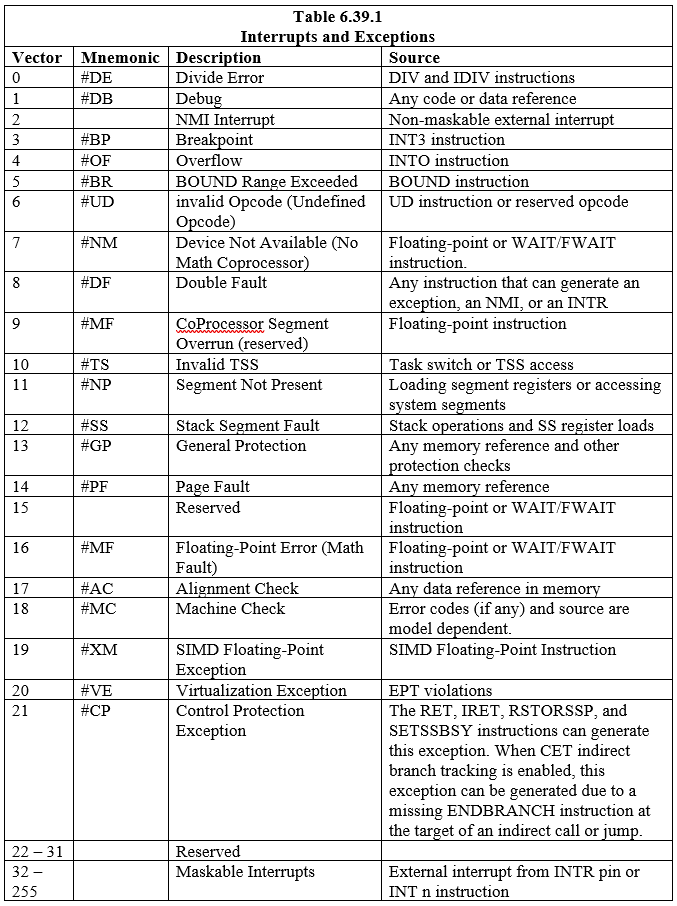

6.39 x64 کے لیے مداخلت اور استثناء

پروسیسر پروگرام کے عمل میں خلل ڈالنے کے لیے دو میکانزم فراہم کرتا ہے، رکاوٹیں، اور مستثنیات:

- ایک مداخلت ایک غیر مطابقت پذیر (کسی بھی وقت ہو سکتا ہے) واقعہ ہے جو عام طور پر I/O ڈیوائس کے ذریعہ متحرک ہوتا ہے۔

- ایک استثنیٰ ایک ہم آہنگی والا واقعہ ہوتا ہے (ایسا ہوتا ہے جب کوڈ کو عمل میں لایا جاتا ہے، پہلے سے پروگرام کیا جاتا ہے، کچھ وقوعہ کی بنیاد پر) جو اس وقت پیدا ہوتا ہے جب پروسیسر کسی ہدایات پر عمل کرتے ہوئے ایک یا زیادہ پہلے سے طے شدہ حالات کا پتہ لگاتا ہے۔ مستثنیات کی تین کلاسیں بیان کی گئی ہیں: فالٹس، ٹریپس، اور اسقاط۔

پروسیسر بنیادی طور پر اسی طرح مداخلتوں اور استثناء کا جواب دیتا ہے۔ جب کسی رکاوٹ یا استثناء کا اشارہ کیا جاتا ہے، تو پروسیسر موجودہ پروگرام یا کام کے عمل کو روکتا ہے اور ہینڈلر کے طریقہ کار پر سوئچ کرتا ہے جو خاص طور پر مداخلت یا استثناء کی حالت کو سنبھالنے کے لیے لکھا جاتا ہے۔ پروسیسر انٹرپٹ ڈسکرپٹر ٹیبل (IDT) میں اندراج کے ذریعے ہینڈلر کے طریقہ کار تک رسائی حاصل کرتا ہے۔ جب ہینڈلر نے مداخلت یا استثنیٰ کو سنبھالنا مکمل کر لیا ہے، تو پروگرام کا کنٹرول رکاوٹ والے پروگرام یا ٹاسک میں واپس آ جاتا ہے۔

آپریٹنگ سسٹم، ایگزیکٹو، اور/یا ڈیوائس ڈرائیور عام طور پر ایپلی کیشن پروگراموں یا کاموں سے آزادانہ طور پر رکاوٹوں اور استثنیٰ کو ہینڈل کرتے ہیں۔ تاہم، ایپلی کیشن پروگرام مداخلت اور استثنیٰ ہینڈلرز تک رسائی حاصل کر سکتے ہیں جو آپریٹنگ سسٹم میں شامل ہیں یا اسمبلی لینگویج کالز کے ذریعے اسے ایگزیکٹو بنا سکتے ہیں۔

اٹھارہ (18) پہلے سے طے شدہ مداخلت اور استثناء، جو IDT میں اندراجات سے وابستہ ہیں، کی وضاحت کی گئی ہے۔ دو سو چوبیس (224) یوزر ڈیفائنڈ انٹرپٹس بھی بنائے جا سکتے ہیں اور ٹیبل کے ساتھ منسلک کیے جا سکتے ہیں۔ IDT میں ہر رکاوٹ اور استثناء کی شناخت ایک نمبر سے کی جاتی ہے جسے 'ویکٹر' کہا جاتا ہے۔ جدول 6.39.1 میں آئی ڈی ٹی اور ان کے متعلقہ ویکٹر میں اندراجات کے ساتھ مداخلت اور استثناء کی فہرست دی گئی ہے۔ ویکٹر 0 سے 8، 10 سے 14، اور 16 سے 19 پہلے سے طے شدہ مداخلت اور استثناء ہیں۔ ویکٹر 32 سے لے کر 255 تک سافٹ وئیر سے طے شدہ انٹرپٹس (صارف) کے لیے ہیں جو یا تو سافٹ ویئر انٹرپٹس یا ماسک ایبل ہارڈویئر انٹرپٹس کے لیے ہیں۔

جب پروسیسر کسی رکاوٹ یا استثناء کا پتہ لگاتا ہے، تو یہ مندرجہ ذیل چیزوں میں سے ایک کرتا ہے:

- ہینڈلر کے طریقہ کار کو ایک مضمر کال پر عمل کریں۔

- ہینڈلر ٹاسک کے لیے ایک مضمر کال پر عمل کریں۔

6.4 64-بٹ ARM کمپیوٹر آرکیٹیکچر کی بنیادی باتیں

اے آر ایم آرکیٹیکچرز RISC پروسیسرز کے خاندان کی وضاحت کرتے ہیں جو ایپلی کیشنز کی وسیع اقسام میں استعمال کے لیے موزوں ہیں۔ اے آر ایم ایک لوڈ/اسٹور آرکیٹیکچر ہے جس کے لیے ڈیٹا کو میموری سے رجسٹر میں لوڈ کرنے کی ضرورت ہوتی ہے اس سے پہلے کہ کوئی پروسیسنگ جیسا کہ ALU (Arithmetic Logic Unit) آپریشن اس کے ساتھ ہوسکتا ہے۔ اس کے بعد کی ہدایت نتیجہ کو واپس میموری میں محفوظ کرتی ہے۔ اگرچہ یہ x86 اور x64 آرکیٹیکچرز سے ایک قدم پیچھے کی طرح لگتا ہے، جو ایک ہی ہدایت میں میموری میں آپرینڈز پر براہ راست کام کرتے ہیں (یقیناً پروسیسر رجسٹر کا استعمال کرتے ہوئے)، عملی طور پر لوڈ/اسٹور کا نقطہ نظر، کئی ترتیب وار کارروائیوں کی اجازت دیتا ہے۔ بہت سے پروسیسر رجسٹروں میں سے کسی ایک میں لوڈ ہونے کے بعد اسے آپرینڈ پر تیز رفتاری سے انجام دیا جائے۔ اے آر ایم پروسیسرز کے پاس بہت کم اینڈیننس یا بڑے اینڈیننس کا آپشن ہوتا ہے۔ ڈیفالٹ ARM 64 سیٹنگ لٹل اینڈین ہے جو کہ وہ کنفیگریشن ہے جو عام طور پر آپریٹنگ سسٹمز کے ذریعہ استعمال ہوتی ہے۔ 64 بٹ اے آر ایم فن تعمیر جدید ہے اور یہ 32 بٹ اے آر ایم آرکیٹیکچر کو تبدیل کرنے کے لیے تیار ہے۔

نوٹ : 64-bit ARM µP کے لیے ہر ہدایت 4 بائٹس (32 بٹس) لمبی ہے۔

6.41 64 بٹ اے آر ایم رجسٹر سیٹ

64-bit ARM µP کے لیے 64-بٹ رجسٹروں کے 31 عمومی مقصد ہیں۔ درج ذیل خاکہ عام مقصد کے رجسٹر اور کچھ اہم رجسٹر دکھاتا ہے:

تصویر 4.11.1 64 بٹ عمومی مقصد اور کچھ اہم رجسٹر

عام مقصد کے رجسٹروں کو X0 سے X30 تک کہا جاتا ہے۔ ہر رجسٹر کے پہلے 32 بٹ حصے کو W0 تا W30 کہا جاتا ہے۔ جب 32 بٹس اور 64 بٹس کے درمیان فرق پر زور نہیں دیا جاتا ہے، تو 'R' کا سابقہ استعمال کیا جاتا ہے۔ مثال کے طور پر، R14 سے مراد W14 یا X14 ہے۔

6502 µP میں 16 بٹ پروگرام کاؤنٹر ہے اور وہ 2 کو ایڈریس کر سکتا ہے۔ 16 میموری بائٹ کے مقامات۔ 64 بٹ ARM µP میں 64 بٹ پروگرام کاؤنٹر ہے اور یہ 2 تک ایڈریس کر سکتا ہے۔ 64 = 1.844674407 x 1019 (دراصل 18,446,744,073,709,551,616) میموری بائٹ کے مقامات۔ پروگرام کاؤنٹر کے پاس اگلی ہدایات کا پتہ ہوتا ہے جس پر عمل کیا جائے۔ ARM64 یا AArch64 کی ہدایات کی لمبائی عام طور پر چار بائٹس ہوتی ہے۔ میموری سے ہر ہدایت حاصل کرنے کے بعد پروسیسر خود بخود اس رجسٹر کو چار تک بڑھاتا ہے۔

اسٹیک پوائنٹر رجسٹر یا ایس پی 31 عام مقصد کے رجسٹروں میں شامل نہیں ہے۔ کسی بھی فن تعمیر کا اسٹیک پوائنٹر میموری میں آخری اسٹیک انٹری کی طرف اشارہ کرتا ہے۔ ARM-64 کے لیے، اسٹیک نیچے کی طرف بڑھتا ہے۔

6502 µP میں 8 بٹ پروسیسر اسٹیٹس رجسٹر ہے۔ ARM64 میں مساوی PSTATE رجسٹر کہلاتا ہے۔ یہ رجسٹر ان جھنڈوں کو محفوظ کرتا ہے جو آپریشن کے نتائج اور پروسیسر (µP) کو کنٹرول کرنے کے لیے استعمال ہوتے ہیں۔ یہ 32 بٹ چوڑا ہے۔ مندرجہ ذیل جدول PSTATE رجسٹر میں عام طور پر استعمال ہونے والے بٹس کے نام، انڈیکس اور معنی دیتا ہے:

| جدول 6.41.1 سب سے زیادہ استعمال ہونے والے PSTATE جھنڈے (بٹس) |

||

|---|---|---|

| علامت | بٹ | مقصد |

| ایم | 0-3 | موڈ: عمل درآمد کی موجودہ استحقاق کی سطح (USR، SVC، اور اسی طرح)۔ |

| ٹی | 4 | انگوٹھا: یہ سیٹ کیا جاتا ہے اگر T32 (انگوٹھا) انسٹرکشن سیٹ فعال ہو۔ اگر واضح ہو تو، ARM انسٹرکشن سیٹ فعال ہے۔ صارف کوڈ اس بٹ کو سیٹ اور صاف کر سکتا ہے۔ |

| اور | 9 | اینڈیننس: اس بٹ کو سیٹ کرنے سے بڑے اینڈین موڈ کو قابل بناتا ہے۔ اگر واضح ہو تو، لٹل اینڈین موڈ فعال ہے۔ ڈیفالٹ لٹل اینڈین موڈ ہے۔ |

| سوال | 27 | مجموعی سنترپتی جھنڈا: یہ سیٹ کیا جاتا ہے اگر، آپریشن کی ایک سیریز میں کسی وقت، ایک اوور فلو یا سنترپتی واقع ہو |

| میں | 28 | اوور فلو فلیگ: یہ سیٹ کیا جاتا ہے اگر آپریشن کے نتیجے میں دستخط شدہ اوور فلو ہوتا ہے۔ |

| سی | 29 | کیری فلیگ: یہ اس بات کی نشاندہی کرتا ہے کہ اس کے اضافے سے کیری پیدا ہوئی یا گھٹانے سے ادھار پیدا ہوا۔ |

| کے ساتھ | 30 | زیرو فلیگ: یہ سیٹ کیا جاتا ہے اگر کسی آپریشن کا نتیجہ صفر ہو۔ |

| ن | 31 | منفی پرچم: یہ سیٹ کیا جاتا ہے اگر کسی آپریشن کا نتیجہ منفی ہو۔ |

ARM-64 µP میں بہت سے دوسرے رجسٹر ہیں۔

سمڈ

SIMD کا مطلب ہے سنگل انسٹرکشن، ایک سے زیادہ ڈیٹا۔ اس کا مطلب یہ ہے کہ اسمبلی کی ایک زبان کی ہدایات ایک مائکرو پروسیسر میں ایک ہی وقت میں متعدد ڈیٹا پر کام کر سکتی ہیں۔ SIMD اور فلوٹنگ پوائنٹ آپریشنز کے ساتھ استعمال کے لیے بتیس 128 بٹس چوڑے رجسٹر ہیں۔

6.42 میموری میپنگ

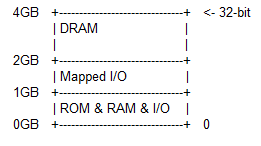

RAM اور DRAM دونوں بے ترتیب رسائی یادیں ہیں۔ DRAM RAM کے مقابلے میں کام میں سست ہے۔ DRAM RAM سے سستا ہے۔ اگر میموری میں جاری DRAM کے 32 گیگا بائٹ (GB) سے زیادہ ہے، تو میموری کے انتظام کے مزید مسائل ہوں گے: 32 GB = 32 x 1024 x 1024 x 1024 بائٹس۔ میموری کی پوری جگہ کے لیے جو 32 GB سے کہیں زیادہ ہے، 32 GB سے اوپر والے DRAM کو میموری کے بہتر انتظام کے لیے RAM کے ساتھ جوڑا جانا چاہیے۔ ARM-64 میموری میپ کو سمجھنے کے لیے، آپ کو پہلے 32-bit ARM سینٹرل پروسیسنگ یونٹ (CPU) کے لیے 4GB میموری میپ کو سمجھنا چاہیے۔ CPU کا مطلب ہے µP۔ 32 بٹ کمپیوٹر کے لیے، زیادہ سے زیادہ میموری ایڈریس ایبل اسپیس 2 ہے۔ 32 = 4 x 2 10 x 2 10 x 2 10 = 4 x 1024 x 1024 x 1024 = 4,294,967,296 = 4GB۔

32 بٹ ARM میموری کا نقشہ

32 بٹ ARM کے لیے میموری کا نقشہ یہ ہے:

32 بٹ کمپیوٹر کے لیے، پوری میموری کا زیادہ سے زیادہ سائز 4 جی بی ہے۔ 0GB ایڈریس سے 1GB ایڈریس تک ROM آپریٹنگ سسٹم، RAM، اور I/O مقامات ہیں۔ ROM OS، RAM، اور I/O ایڈریس کا پورا خیال ممکنہ 6502 CPU کے ساتھ کموڈور-64 کی صورت حال سے ملتا جلتا ہے۔ کموڈور-64 کے لیے OS ROM میموری کی جگہ کے اوپری حصے میں ہے۔ یہاں کا ROM OS کموڈور-64 سے بہت بڑا ہے، اور یہ پوری میموری ایڈریس اسپیس کے شروع میں ہے۔ جب دوسرے جدید کمپیوٹرز سے موازنہ کیا جائے تو یہاں ROM OS مکمل ہے، اس لحاظ سے کہ یہ ان کی ہارڈ ڈرائیوز میں OS کی مقدار سے موازنہ ہے۔ ROM انٹیگریٹڈ سرکٹس میں OS رکھنے کی دو اہم وجوہات ہیں: 1) ARM CPUs زیادہ تر اسمارٹ فونز جیسے چھوٹے آلات میں استعمال ہوتے ہیں۔ بہت سی ہارڈ ڈرائیوز اسمارٹ فونز اور دیگر چھوٹے آلات سے بڑی ہوتی ہیں، 2) سیکیورٹی کے لیے۔ جب OS صرف پڑھنے کی میموری میں ہوتا ہے، تو اسے ہیکرز کے ذریعے خراب نہیں کیا جا سکتا (پرزے اوور رائٹ)۔ کموڈور-64 کے مقابلے میں رام سیکشنز اور ان پٹ/آؤٹ پٹ سیکشنز بھی بہت بڑے ہیں۔

جب 32 بٹ ROM OS کے ساتھ پاور آن کی جاتی ہے، تو OS کو 0x00000000 ایڈریس یا 0xFFFF0000 ایڈریس سے شروع ہونا چاہیے اگر HiVECs فعال ہو۔ لہذا، جب ری سیٹ کے مرحلے کے بعد پاور آن کی جاتی ہے، تو CPU ہارڈویئر 0x00000000 یا 0xFFFF0000 کو پروگرام کاؤنٹر پر لوڈ کرتا ہے۔ '0x' سابقہ کا مطلب ہیکساڈیسیمل ہے۔ ARMv8 64bit CPUs کا بوٹ ایڈریس ایک متعین نفاذ ہے۔ تاہم، مصنف نے کمپیوٹر انجینئر کو مشورہ دیا ہے کہ وہ پسماندہ مطابقت کی خاطر 0x00000000 یا 0xFFFF0000 سے شروع کریں۔

1GB سے 2GB تک میپ شدہ ان پٹ/آؤٹ پٹ ہے۔ میپ شدہ I/O اور صرف I/O کے درمیان فرق ہے جو 0GB اور 1GB کے درمیان پائے جاتے ہیں۔ I/O کے ساتھ، ہر بندرگاہ کا پتہ کموڈور-64 کے ساتھ طے ہوتا ہے۔ میپڈ I/O کے ساتھ، ضروری نہیں کہ ہر پورٹ کا پتہ کمپیوٹر کے ہر آپریشن (متحرک) کے لیے ایک جیسا ہو۔

2GB سے 4GB تک DRAM ہے۔ یہ متوقع (یا معمول کی) RAM ہے۔ DRAM کا مطلب ہے Dynamic RAM، کمپیوٹر آپریشن کے دوران بدلتے ہوئے پتہ کا احساس نہیں ہے بلکہ اس معنی میں ہے کہ جسمانی RAM میں ہر سیل کی قدر کو ہر گھڑی کی نبض پر تازہ کرنا ہوتا ہے۔

نوٹ :

- 0x0000,0000 سے 0x0000 تک، FFFF OS ROM ہے۔

- 0x0001,0000 سے 0x3FFF، FFFF تک، مزید ROM، پھر RAM، اور پھر کچھ I/O ہو سکتے ہیں۔

- 0x4000,0000 سے 0x7FFF،FFFF، ایک اضافی I/O اور/یا میپ شدہ I/O کی اجازت ہے۔

- 0x8000,0000 سے 0xFFFF تک، FFFF متوقع DRAM ہے۔

اس کا مطلب یہ ہے کہ متوقع DRAM کو عملی طور پر 2GB میموری باؤنڈری سے شروع نہیں ہونا چاہیے۔ پروگرامر کو مثالی حدود کا احترام کیوں کرنا چاہئے جب کافی جسمانی RAM بینک نہیں ہیں جو مدر بورڈ پر سلاٹ ہیں؟ اس کی وجہ یہ ہے کہ صارف کے پاس تمام RAM بینکوں کے لیے کافی رقم نہیں ہے۔

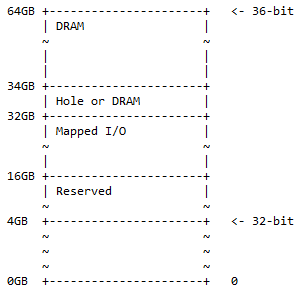

36 بٹ ARM میموری کا نقشہ

64 بٹ اے آر ایم کمپیوٹر کے لیے، تمام 32 بٹس پوری میموری کو ایڈریس کرنے کے لیے استعمال کیے جاتے ہیں۔ 64 بٹ اے آر ایم کمپیوٹر کے لیے، پہلے 36 بٹس کو پوری میموری کو ایڈریس کرنے کے لیے استعمال کیا جا سکتا ہے جو کہ اس معاملے میں 2 ہے۔ 36 = 68,719,476,736 = 64GB۔ یہ پہلے ہی بہت زیادہ میموری ہے۔ عام کمپیوٹرز کو آج اس مقدار میں میموری کی ضرورت نہیں ہے۔ یہ ابھی تک میموری کی زیادہ سے زیادہ حد تک نہیں ہے جس تک 64 بٹس تک رسائی حاصل کی جا سکتی ہے۔ ARM CPU کے لیے 36 بٹس کے لیے میموری کا نقشہ یہ ہے:

0GB ایڈریس سے 4GB ایڈریس تک 32 بٹ میموری میپ ہے۔ 'محفوظ' کا مطلب ہے استعمال نہیں کیا گیا اور اسے مستقبل کے استعمال کے لیے رکھا گیا ہے۔ ضروری نہیں ہے کہ یہ فزیکل میموری بینک ہوں جو اس جگہ کے لیے مدر بورڈ پر سلاٹ ہوں۔ یہاں، DRAM اور میپڈ I/O کے وہی معنی ہیں جو 32 بٹ میموری میپ کے ہیں۔

مندرجہ ذیل صورت حال عملی طور پر پایا جا سکتا ہے:

- 0x1 0000 0000 - 0x3 FFFF FFFF؛ محفوظ 12GB پتے کی جگہ مستقبل کے استعمال کے لیے مختص ہے۔

- 0x4 0000 0000 - 0x7 FFFF FFFF؛ نقشہ شدہ I/O 16GB ایڈریس کی جگہ متحرک طور پر نقشہ کردہ I/O کے لیے دستیاب ہے۔

- 0x8 0000 0000 - 0x8 7FFF FFFF FFFF; سوراخ یا DRAM۔ 2 جی بی ایڈریس اسپیس میں درج ذیل میں سے کسی ایک پر مشتمل ہوسکتا ہے:

- DRAM ڈیوائس کی تقسیم کو فعال کرنے کے لیے سوراخ (جیسا کہ مندرجہ ذیل بحث میں بیان کیا گیا ہے)۔

- ڈرام

- 0x8 8000 0000 - 0xF FFFF FFFF; ڈرام DRAM کے لیے 30GB پتے کی جگہ۔

یہ میموری میپ 32 بٹ ایڈریس میپ کا ایک سپر سیٹ ہے، جس میں اضافی جگہ کو 50% DRAM (1/2) کے طور پر تقسیم کیا گیا ہے جس میں اختیاری سوراخ ہے اور 25% میپ شدہ I/O اسپیس اور مخصوص جگہ (1/4) )۔ بقیہ 25% (1/4) 32 بٹ میموری میپ ½ + ¼ + ¼ = 1 کے لیے ہے۔

نوٹ : 32 بٹس سے 360 بٹس 36 بٹس کے سب سے اہم پہلو میں 4 بٹس کا اضافہ ہے۔

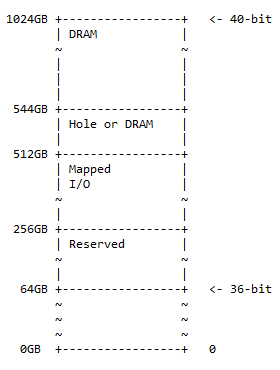

40 بٹ میموری کا نقشہ

40 بٹ ایڈریس میپ 36 بٹ ایڈریس میپ کا ایک سپر سیٹ ہے اور اس میں اختیاری سوراخ کے 50% DRAM کے اسی پیٹرن کی پیروی کرتا ہے، 25% میپ شدہ I/O اسپیس اور محفوظ جگہ، اور باقی 25% پچھلے میموری نقشے کے لیے جگہ (36 بٹ)۔ میموری نقشہ کا خاکہ یہ ہے:

سوراخ کا سائز 544 - 512 = 32GB ہے۔ مندرجہ ذیل صورت حال عملی طور پر پایا جا سکتا ہے:

- 0x10 0000 0000 - 0x3F FFFF FFFF; محفوظ 192GB پتے کی جگہ مستقبل کے استعمال کے لیے مختص ہے۔

- 0x40 0000 0000 - 0x7F FFFF FFFF; نقشہ بنایا I/O 256GB ایڈریس کی جگہ متحرک طور پر نقشہ کردہ I/O کے لیے دستیاب ہے۔

- 0x80 0000 0000 - 0x87 FFFF FFFF; سوراخ یا DRAM۔ 32 جی بی ایڈریس اسپیس میں درج ذیل میں سے کسی ایک پر مشتمل ہوسکتا ہے:

- DRAM ڈیوائس پارٹیشننگ کو فعال کرنے کے لیے سوراخ (جیسا کہ درج ذیل بحث میں بیان کیا گیا ہے)

- ڈرام

- 0x88 0000 0000 - 0xFF FFFF FFFF; ڈرام DRAM کے لیے 480GB پتہ کی جگہ۔

نوٹ : 36 بٹس سے 40 بٹس 36 بٹس کے سب سے اہم پہلو میں 4 بٹس کا اضافہ ہے۔

DRAM ہول

میموری میپ میں 32 بٹس سے آگے، یہ یا تو DRAM ہول ہے یا اوپر سے DRAM کا تسلسل ہے۔ جب یہ ایک سوراخ ہے، تو اس کی تعریف اس طرح کی جانی چاہیے: DRAM ہول ایک بڑے DRAM ڈیوائس کو متعدد ایڈریس رینجز میں تقسیم کرنے کا طریقہ فراہم کرتا ہے۔ اختیاری DRAM سوراخ اعلی DRAM ایڈریس باؤنڈری کے آغاز میں تجویز کیا جاتا ہے۔ یہ ایک آسان ڈی کوڈنگ اسکیم کو قابل بناتا ہے جب بڑی صلاحیت والے DRAM ڈیوائس کو نچلے جسمانی طور پر ایڈریس والے علاقے میں تقسیم کیا جاتا ہے۔

مثال کے طور پر، ایک 64GB DRAM حصے کو تین خطوں میں ذیلی تقسیم کیا گیا ہے جس میں ایڈریس آفسیٹس کو ہائی آرڈر ایڈریس بٹس میں ایک سادہ گھٹاؤ کے ذریعے انجام دیا جاتا ہے:

| جدول 6.42.1 سوراخوں کے ساتھ 64GB DRAM پارٹیشننگ کی مثال |

|||

|---|---|---|---|

| SoC میں جسمانی پتے | آفسیٹ | اندرونی DRAM پتہ | |

| 2 GBytes (32 بٹ نقشہ) | 0x00 8000 0000 - 0x00 FFFF FFFF | -0x00 8000 0000 | 0x00 0000 0000 - 0x00 7FFF FFFF |

| 30 GBytes (36 بٹ نقشہ) | 0x08 8000 0000 - 0x0F FFFF FFFF | -0x08 0000 0000 | 0x00 8000 0000 - 0x07 FFFF FFFF |

| 32 GBytes (40 بٹ نقشہ) | 0x88 0000 0000 - 0x8F FFFF FFFF | -0x80 0000 0000 | 0x08 0000 0000 - 0x0F FFFF FFFF |

ARM CPUs کے لیے مجوزہ 44 بٹ اور 48 بٹ ایڈریسڈ میموری میپس

فرض کریں کہ ایک پرسنل کمپیوٹر میں 1024GB (= 1TB) میموری ہے۔ یہ بہت زیادہ میموری ہے. اور اس طرح، ARM CPUs کے لیے بالترتیب 16 TB اور 256 TB کے لیے 44-bit اور 48-bit ایڈریسڈ میموری نقشے، مستقبل کے کمپیوٹر کی ضروریات کے لیے صرف تجاویز ہیں۔ درحقیقت، ARM CPUs کے لیے یہ تجاویز پچھلے میموری نقشوں کے تناسب کے لحاظ سے میموری کی اسی تقسیم کی پیروی کرتی ہیں۔ یعنی: 50% DRAM اس میں اختیاری سوراخ کے ساتھ، 25% میپ شدہ I/O اسپیس اور ریزروڈ اسپیس، اور بقیہ 25% جگہ پچھلے میموری میپ کے لیے۔

52-bit، 56-bit، 60-bit اور 64-bit ایڈریسڈ میموری نقشے ابھی دور مستقبل کے لیے ARM 64 بٹس کے لیے تجویز کیے جانے ہیں۔ اگر اس وقت کے سائنسدانوں کو پوری میموری کی جگہ کی 50 : 25 : 25 تقسیم کارآمد معلوم ہوتی ہے تو وہ اس تناسب کو برقرار رکھیں گے۔

نوٹ : ایس او سی کا مطلب ہے سسٹم آن چپ جس سے مراد µP چپ میں موجود سرکٹس ہیں جو دوسری صورت میں وہاں نہ ہوتے۔

SRAM یا Static Random Access Memory زیادہ روایتی DRAM سے تیز ہے، لیکن اس کے لیے زیادہ سلکان ایریا کی ضرورت ہوتی ہے۔ SRAM کو تازگی کی ضرورت نہیں ہے۔ ریڈر رام کو SRAM کے طور پر تصور کر سکتا ہے۔

6.43 ARM 64 کے لیے اسمبلی لینگویج ایڈریسنگ موڈز

اے آر ایم ایک لوڈ/اسٹور آرکیٹیکچر ہے جس کے لیے ڈیٹا کو میموری سے پروسیسر رجسٹر میں لوڈ کرنے کی ضرورت ہوتی ہے اس سے پہلے کہ اس کے ساتھ کوئی بھی پروسیسنگ جیسا کہ ریاضی منطقی آپریشن ہو سکے۔ اس کے بعد کی ہدایت نتیجہ کو واپس میموری میں محفوظ کرتی ہے۔ اگرچہ یہ x86 اور اس کے بعد کے x64 آرکیٹیکچرز سے ایک قدم پیچھے کی طرح لگتا ہے، جو ایک ہی ہدایات میں میموری میں آپرینڈز پر براہ راست کام کرتے ہیں، عملی طور پر، لوڈ/اسٹور اپروچ کئی ترتیب وار آپریشنز کو تیز رفتاری سے انجام دینے کی اجازت دیتا ہے۔ ایک آپرینڈ ایک بار جب یہ بہت سے پروسیسر رجسٹروں میں سے ایک میں لوڈ ہو جاتا ہے۔

اے آر ایم اسمبلی لینگویج کے فارمیٹ میں x64 (x86) سیریز کے ساتھ مماثلت اور فرق ہے۔

- آفسیٹ : ایک دستخط شدہ مستقل کو بیس رجسٹر میں شامل کیا جا سکتا ہے۔ آفسیٹ کو ہدایات کے حصے کے طور پر ٹائپ کیا گیا ہے۔ مثال کے طور پر: ldr x0, [rx, #10] r1+10 ایڈریس پر لفظ کے ساتھ r0 لوڈ کرتا ہے۔

- رجسٹر کریں۔ : ایک غیر دستخط شدہ اضافہ جو کہ ایک رجسٹر میں ذخیرہ کیا جاتا ہے کو بیس رجسٹر میں موجود قیمت میں شامل یا گھٹایا جا سکتا ہے۔ مثال کے طور پر: ldr r0, [x1, x2] r0 کو x1+x2 ایڈریس پر لفظ کے ساتھ لوڈ کرتا ہے۔ کسی بھی رجسٹر کو بیس رجسٹر کے طور پر سوچا جا سکتا ہے۔

- اسکیلڈ رجسٹر : بنیادی رجسٹر ویلیو میں شامل یا گھٹانے سے پہلے ایک رجسٹر میں اضافہ کو بٹ پوزیشنوں کی ایک مخصوص تعداد کے ذریعے بائیں یا دائیں منتقل کیا جاتا ہے۔ مثال کے طور پر: ldr x0, [x1, x2, lsl #3] r1+(r2×8) ایڈریس پر r0 کو لفظ کے ساتھ لوڈ کرتا ہے۔ شفٹ ایک منطقی بائیں یا دائیں شفٹ (lsl یا lsr) ہو سکتی ہے جو خالی جگہوں پر صفر بٹس داخل کرتی ہے یا ریاضی کی دائیں شفٹ (asr) جو خالی جگہوں پر سائن بٹ کو نقل کرتی ہے۔

جب دو آپرینڈز شامل ہوتے ہیں، تو منزل (بائیں طرف) ماخذ سے پہلے آتی ہے (اس میں کچھ مستثنیات ہیں)۔ اے آر ایم اسمبلی لینگویج کے اوپکوڈز کیس غیر حساس ہیں۔

فوری ARM64 ایڈریسنگ موڈ

مثال:

mov r0, #0xFF000000 ; 32 بٹ ویلیو FF000000h کو r0 میں لوڈ کریں۔

اعشاریہ کی قدر 0x کے بغیر ہے لیکن پھر بھی # سے پہلے ہے۔

براہ راست رجسٹر کریں۔

مثال:

mov x0, x1 ; x1 کو x0 میں کاپی کریں۔

بالواسطہ رجسٹر کریں۔

مثال:

str x0, [x3] ; x0 کو x3 میں ایڈریس پر اسٹور کریں۔

آفسیٹ کے ساتھ بالواسطہ رجسٹر کریں۔

مثالیں:

ldr x0, [x1, #32] ; r0 کو ایڈریس پر ویلیو کے ساتھ لوڈ کریں [r1+32]؛ r1 بنیادی رجسٹر ہے۔

str x0, [x1, #4] ; r0 کو ایڈریس پر اسٹور کریں [r1+4]؛ r1 بنیادی رجسٹر ہے۔ نمبر بیس 10 ہیں۔

آف سیٹ کے ساتھ بالواسطہ رجسٹر کریں (پہلے سے بڑھے ہوئے)

مثالیں:

ldr x0, [x1, #32]! ; r0 کو [r1+32] کے ساتھ لوڈ کریں اور r1 کو (r1+32) میں اپ ڈیٹ کریں

str x0, [x1, #4]! ; r0 کو [r1+4] میں اسٹور کریں اور r1 کو (r1+4) میں اپ ڈیٹ کریں

'!' کے استعمال کو نوٹ کریں۔ علامت

آفسیٹ کے ساتھ بالواسطہ رجسٹر کریں (پوسٹ انکریمنٹڈ)

مثالیں:

ldr x0, [x1], #32 ; [x1] کو x0 پر لوڈ کریں، پھر x1 کو (x1+32) میں اپ ڈیٹ کریں

str x0, [x1], #4 ; x0 سے [x1] کو اسٹور کریں، پھر x1 کو (x1+4) میں اپ ڈیٹ کریں

بالواسطہ ڈبل رجسٹر کریں۔

آپرینڈ کا پتہ بیس رجسٹر اور انکریمنٹ رجسٹر کا مجموعہ ہے۔ رجسٹر کے نام مربع بریکٹ سے گھرے ہوئے ہیں۔

مثالیں:

ldr x0, [x1, x2] ; x0 لوڈ کریں [x1+x2] کے ساتھ

str x0, [rx, x2] ; اسٹور x0 سے [x1+x2]

رشتہ دار ایڈریسنگ موڈ

رشتہ دار ایڈریسنگ موڈ میں، مؤثر ہدایات پروگرام کاؤنٹر میں اگلی ہدایت ہے، نیز ایک اشاریہ۔ انڈیکس مثبت یا منفی ہو سکتا ہے۔

مثال:

ldr x0, [pc, #24]

اس کا مطلب ہے لوڈ رجسٹر X0 اس لفظ کے ساتھ جس کی طرف PC مواد پلس 24 کی طرف اشارہ کیا گیا ہے۔

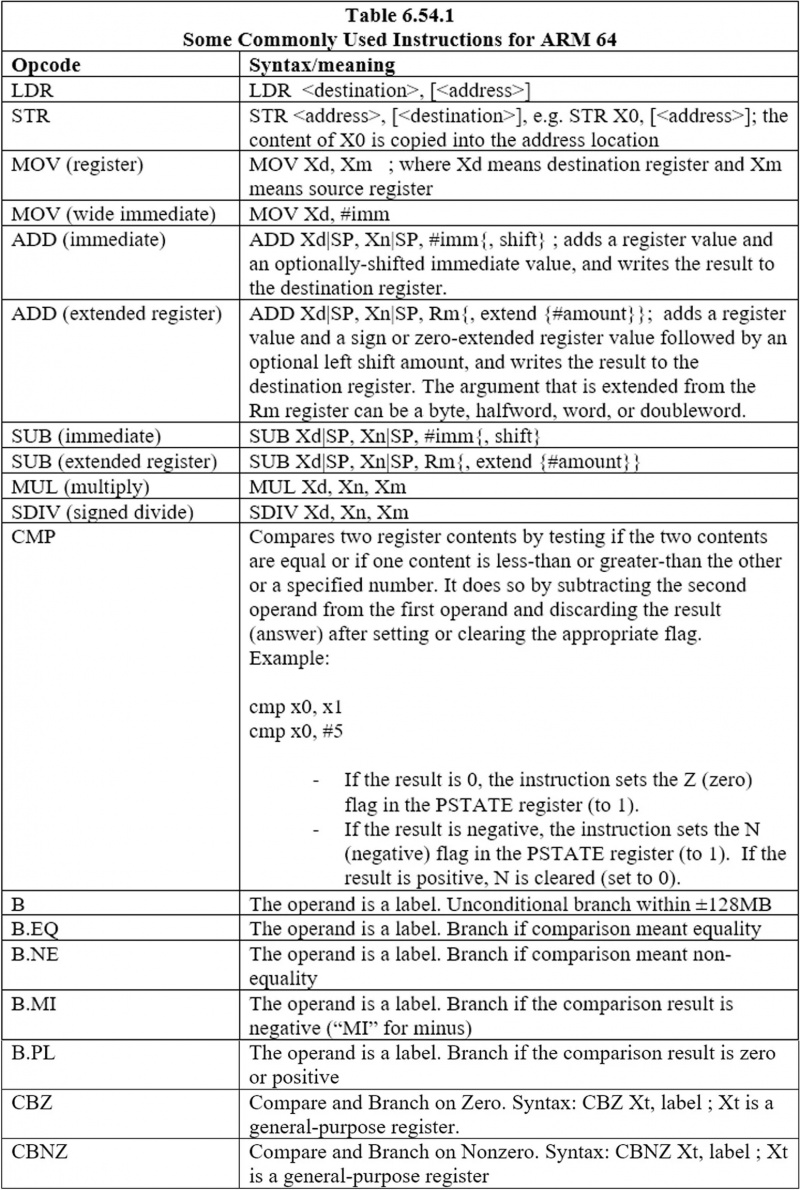

6.44 ARM 64 کے لیے عام طور پر استعمال ہونے والی کچھ ہدایات

یہاں عام طور پر استعمال ہونے والی ہدایات ہیں:

6.45 لوپنگ

مثال

مندرجہ ذیل کوڈ X10 رجسٹر میں موجود ویلیو کو X9 کی ویلیو میں شامل کرتا رہتا ہے جب تک کہ X8 میں ویلیو صفر نہ ہو جائے۔ فرض کریں کہ تمام اقدار عددی ہیں۔ X8 میں قدر کو ہر تکرار میں 1 سے گھٹایا جاتا ہے:

لوپ:

CBZ X8، چھوڑیں۔

X9، X9، X10 شامل کریں؛ پہلا X9 منزل ہے اور دوسرا X9 ذریعہ ہے۔

SUB X8, X8, #1 ; پہلا X8 منزل ہے اور دوسرا X8 ذریعہ ہے۔

بی لوپ

چھوڑ دو:

6502 µP اور X64 µP کی طرح، ARM 64 µP میں لیبل لائن کے آغاز سے شروع ہوتا ہے۔ باقی ہدایات لائن کے آغاز کے بعد کچھ جگہوں پر شروع ہوتی ہیں۔ x64 اور ARM 64 کے ساتھ، لیبل کے بعد بڑی آنت اور ایک نئی لائن آتی ہے۔ جبکہ 6502 کے ساتھ، لیبل کے بعد اسپیس کے بعد ایک ہدایت ہوتی ہے۔ پچھلے کوڈ میں، پہلی ہدایات جو ہے 'CBZ X8، skip' کا مطلب ہے کہ اگر X8 میں قدر صفر ہے، تو 'skip:' لیبل پر جاری رکھیں، درمیان میں دی گئی ہدایات کو چھوڑ کر اور نیچے دی گئی باقی ہدایات کے ساتھ جاری رکھیں۔ 'چھوڑ دو:'. 'B لوپ' 'لوپ' لیبل پر ایک غیر مشروط چھلانگ ہے۔ کسی بھی دوسرے لیبل کا نام 'لوپ' کی جگہ استعمال کیا جا سکتا ہے۔

لہذا، 6502 µP کی طرح، ARM 64 کے ساتھ ایک لوپ رکھنے کے لیے برانچ کی ہدایات کا استعمال کریں۔

6.46 ARM 64 ان پٹ/آؤٹ پٹ

تمام ARM پیری فیرلز (اندرونی پورٹس) میموری میپڈ ہیں۔ اس کا مطلب ہے کہ پروگرامنگ انٹرفیس میموری ایڈریس شدہ رجسٹر (اندرونی پورٹس) کا ایک سیٹ ہے۔ ایسے رجسٹر کا پتہ مخصوص میموری بیس ایڈریس سے ایک آفسیٹ ہوتا ہے۔ یہ اسی طرح ہے جس طرح 6502 ان پٹ/آؤٹ پٹ کرتا ہے۔ ARM کے پاس علیحدہ I/O پتہ کی جگہ کا اختیار نہیں ہے۔

ARM 64 کا 6.47 اسٹیک

ARM 64 میں میموری (RAM) میں اسٹیک اسی طرح ہے جس طرح 6502 اور x64 میں ہے۔ تاہم، ARM64 کے ساتھ، کوئی پش یا پاپ اوپکوڈ نہیں ہے۔ ARM 64 میں اسٹیک بھی نیچے کی طرف بڑھتا ہے۔ اسٹیک پوائنٹر میں ایڈریس اسٹیک میں رکھی گئی آخری قدر کے آخری بائٹ کے عین بعد پوائنٹ کرتا ہے۔

ARM64 کے لیے کوئی عام پاپ یا پش اوپک کوڈ نہ ہونے کی وجہ یہ ہے کہ ARM 64 اپنے اسٹیک کو لگاتار 16 بائٹس کے گروپس میں منظم کرتا ہے۔ تاہم، اقدار ایک بائٹ، دو بائٹس، چار بائٹس، اور 8 بائٹس کے بائٹ گروپس میں موجود ہیں۔ لہذا، ایک قدر اسٹیک میں رکھی جا سکتی ہے، اور باقی جگہیں (بائٹ لوکیشنز) 16 بائٹس بنانے کے لیے ڈمی بائٹس کے ساتھ پیڈ کی جاتی ہیں۔ اس سے یادداشت ضائع ہونے کا نقصان ہے۔ ایک بہتر حل یہ ہے کہ 16 بائٹ والے مقام کو چھوٹی قدروں سے پُر کیا جائے اور اس میں کچھ پروگرامر تحریری کوڈ ہو جو یہ ٹریک کرتا ہے کہ 16 بائٹ والے مقام کی قدریں کہاں سے آتی ہیں (رجسٹرز)۔ اس اضافی کوڈ کی قدروں کو واپس لینے میں بھی ضرورت ہے۔ اس کا متبادل یہ ہے کہ 8 بائٹ کے دو عمومی مقصد کے رجسٹروں کو مختلف اقدار کے ساتھ پُر کریں، اور پھر دو 8 بائٹ رجسٹروں کے مواد کو اسٹیک پر بھیجیں۔ اسٹیک میں جانے والی مخصوص چھوٹی اقدار کو ٹریک کرنے اور اسٹیک کو چھوڑنے کے لیے یہاں ایک اضافی کوڈ کی ضرورت ہے۔

درج ذیل کوڈ اسٹیک میں چار 4 بائٹ ڈیٹا اسٹور کرتا ہے۔

str w0, [sp, #-4]!

str w1, [sp, #-8]!

str w2, [sp, #-12]!

str w3, [sp, #-16]!

رجسٹروں کے پہلے چار بائٹس (w) - x0, x1, x2, اور x3 - کو اسٹیک میں لگاتار 16-بائٹ مقامات پر بھیجا جاتا ہے۔ 'str' کا استعمال نوٹ کریں نہ کہ 'دھکا'۔ ہر ہدایت کے آخر میں فجائیہ کی علامت کو نوٹ کریں۔ چونکہ میموری اسٹیک نیچے کی طرف بڑھتا ہے، اس لیے پہلی فور بائٹ ویلیو اس پوزیشن سے شروع ہوتی ہے جو پچھلی اسٹیک پوائنٹر پوزیشن سے مائنس فور بائٹس نیچے ہے۔ چار بائٹ کی باقی اقدار نیچے جا رہی ہیں۔ درج ذیل کوڈ سیگمنٹ درست (اور ترتیب میں) چار بائٹس کو پاپ کرنے کے برابر کرے گا:

ldr w3, [sp], #0

ldr w2، [sp]، #4

ldr w1، [sp]، #8

ldr w0, [sp], #12

پاپ کے بجائے ldr opcode کا استعمال نوٹ کریں۔ یہ بھی نوٹ کریں کہ یہاں فجائیہ کی علامت استعمال نہیں کی گئی ہے۔

X0 (8 بائٹس) اور X1 (8 بائٹس) میں موجود تمام بائٹس کو اسٹیک میں 16 بائٹ لوکیشن پر اس طرح بھیجا جا سکتا ہے:

stp x0, x1, [sp, #-16]! ; 8 + 8 = 16

اس صورت میں، x2 (w2) اور x3 (w3) رجسٹروں کی ضرورت نہیں ہے۔ تمام مطلوبہ بائٹس X0 اور X2 رجسٹروں میں ہیں۔ رجسٹر مواد کے جوڑے کو رام میں ذخیرہ کرنے کے لیے stp opcode کو نوٹ کریں۔ فجائیہ کی علامت بھی نوٹ کریں۔ پاپ کے برابر ہے:

ldp x0, x1, [sp], #0

اس ہدایت کے لیے کوئی فجائیہ نشان نہیں ہے۔ میموری سے دو µP رجسٹروں پر لگاتار دو ڈیٹا لوکیشن لوڈ کرنے کے لیے LDR کے بجائے اوپکوڈ LDP کو نوٹ کریں۔ یہ بھی یاد رکھیں کہ میموری سے µP رجسٹر میں کاپی کرنا لوڈ ہو رہا ہے، ڈسک سے RAM پر فائل لوڈ کرنے کے ساتھ الجھن میں نہ پڑیں، اور µP رجسٹر سے RAM میں کاپی کرنا اسٹور ہو رہا ہے۔

6.48 سب روٹین

سب روٹین کوڈ کا ایک بلاک ہے جو ایک کام انجام دیتا ہے، اختیاری طور پر کچھ دلائل کی بنیاد پر اور اختیاری طور پر نتیجہ واپس کرتا ہے۔ کنونشن کے مطابق، R0 سے R3 رجسٹر (چار رجسٹر) کا استعمال دلائل (پیرامیٹر) کو سب روٹین میں منتقل کرنے کے لیے کیا جاتا ہے، اور R0 کو کال کرنے والے کو نتیجہ واپس بھیجنے کے لیے استعمال کیا جاتا ہے۔ ایک سب روٹین جس کو 4 سے زیادہ ان پٹس کی ضرورت ہوتی ہے وہ اضافی ان پٹس کے لیے اسٹیک کا استعمال کرتا ہے۔ سب روٹین کو کال کرنے کے لیے، لنک یا مشروط برانچ کی ہدایات کا استعمال کریں۔ لنک ہدایات کے لیے نحو ہے:

بی ایل لیبل

جہاں BL opcode ہے اور لیبل سب روٹین کے آغاز (پتہ) کی نمائندگی کرتا ہے۔ یہ برانچ 128MB کے اندر غیر مشروط، آگے یا پیچھے ہے۔ مشروط شاخ کی ہدایات کے لیے نحو ہے:

B.cond لیبل

جہاں cond شرط ہے، جیسے، eq (برابر) یا ne (برابر نہیں)۔ درج ذیل پروگرام میں doadd سبروٹین ہے جو دو دلائل کی قدروں کو جوڑتا ہے اور نتیجہ R0 میں دیتا ہے:

AREA subrout, CODE, READONLY ; کوڈ کے اس بلاک کو نام دیں۔

داخلہ ؛ عمل کرنے کے لیے پہلی ہدایات کو نشان زد کریں۔

شروع کریں MOV r0, #10 ; پیرامیٹرز مرتب کریں۔

MOV r1, #3

BL doadd ; سب روٹین کو کال کریں۔

روکیں MOV r0, #0x18 ; angel_SWIreason_ReportException

LDR r1, =0x20026 ; ADP_Stopped_Application Exit

SVC #0x123456 ; ARM سیمی ہوسٹنگ (سابقہ SWI)

doadd ADD r0, r0, r1 ; سب روٹین کوڈ

BX lr ; سب روٹین سے واپسی

;

اختتام ; فائل کے اختتام کو نشان زد کریں۔

شامل کرنے کے لیے اعداد اعشاریہ 10 اور اعشاریہ 3 ہیں۔ کوڈ کے اس بلاک (پروگرام) میں پہلی دو لائنوں کی وضاحت بعد میں کی جائے گی۔ اگلی تین لائنیں 10 کو R0 رجسٹر اور 3 کو R1 رجسٹر بھیجتی ہیں، اور doadd subroutine کو بھی کال کرتی ہیں۔ 'doadd' وہ لیبل ہے جو سب روٹین کے آغاز کا پتہ رکھتا ہے۔

سب روٹین صرف دو لائنوں پر مشتمل ہے۔ پہلی لائن R0 کے مواد 10 میں R کے مواد 3 کا اضافہ کرتی ہے جو R0 میں 13 کے نتیجے کی اجازت دیتی ہے۔ BX opcode اور LR آپرینڈ کے ساتھ دوسری لائن سب روٹین سے کالر کوڈ پر واپس آتی ہے۔

حق

ARM 64 میں RET opcode اب بھی سب روٹین سے نمٹتا ہے، لیکن 6502 میں RTS یا x64 پر RET، یا ARM 64 میں 'BX LR' مجموعہ سے مختلف طریقے سے کام کرتا ہے۔ ARM 64 میں، RET کا نحو ہے:

سیدھا {Xn}

یہ ہدایت پروگرام کو ایک سب روٹین کے ساتھ جاری رکھنے کا موقع فراہم کرتی ہے جو کالر سب روٹین نہیں ہے، یا صرف کسی اور ہدایات اور اس کے درج ذیل کوڈ سیگمنٹ کے ساتھ جاری رکھیں۔ Xn ایک عام مقصد کا رجسٹر ہے جس میں وہ پتہ ہوتا ہے جس پر پروگرام کو جاری رکھنا چاہیے۔ یہ ہدایت غیر مشروط طور پر برانچ کرتی ہے۔ اگر Xn نہیں دیا جاتا ہے تو یہ X30 کے مواد سے پہلے سے طے شدہ ہے۔

طریقہ کار کال سٹینڈرڈ

اگر پروگرامر چاہتا ہے کہ اس کا کوڈ کسی دوسرے کے لکھے ہوئے کوڈ کے ساتھ یا کسی کمپائلر کے تیار کردہ کوڈ کے ساتھ تعامل کرے، تو پروگرامر کو رجسٹر کے استعمال کے قواعد پر اس شخص یا کمپائلر مصنف سے اتفاق کرنا ہوگا۔ اے آر ایم آرکیٹیکچر کے لیے، ان اصولوں کو پروسیجر کال اسٹینڈرڈ یا پی سی ایس کہا جاتا ہے۔ یہ دو یا تین فریقوں کے درمیان معاہدے ہیں۔ PCS مندرجہ ذیل کی وضاحت کرتا ہے:

- کون سے µP رجسٹروں کو فنکشن (سب روٹین) میں دلائل منتقل کرنے کے لیے استعمال کیا جاتا ہے

- کون سے µP رجسٹروں کا استعمال نتیجہ کو اس فنکشن میں واپس کرنے کے لیے کیا جاتا ہے جو کالنگ کرتا ہے جسے کالر کے نام سے جانا جاتا ہے

- کون سا µP اس فنکشن کو رجسٹر کرتا ہے جسے کال کیا جا رہا ہے، جسے کالی کہا جاتا ہے، کرپٹ ہو سکتا ہے

- کون سا µP رجسٹر کرتا ہے کالی بدعنوانی نہیں کرسکتا

6.49 رکاوٹیں

ARM پروسیسر کے لیے دو قسم کے انٹرپٹ کنٹرولر سرکٹس دستیاب ہیں:

- سٹینڈرڈ انٹرپٹ کنٹرولر: انٹرپٹ ہینڈلر انٹرپٹ کنٹرولر میں ڈیوائس بٹ میپ رجسٹر پڑھ کر تعین کرتا ہے کہ کس ڈیوائس کو سروسنگ کی ضرورت ہے۔

- ویکٹر انٹرپٹ کنٹرولر (VIC): مداخلتوں کو ترجیح دیتا ہے اور اس بات کے تعین کو آسان بناتا ہے کہ کس ڈیوائس نے رکاوٹ پیدا کی۔ ہر ایک انٹرپٹ کے ساتھ ترجیح اور ہینڈلر ایڈریس کو منسلک کرنے کے بعد، VIC صرف اس صورت میں پروسیسر کو ایک انٹرپٹ سگنل دیتا ہے جب کسی نئے انٹرپٹ کی ترجیح اس وقت عمل میں آنے والے انٹرپٹ ہینڈلر سے زیادہ ہو۔

نوٹ : استثناء سے مراد غلطی ہے۔ 32 بٹ اے آر ایم کمپیوٹر کے ویکٹر انٹرپٹ کنٹرولر کی تفصیلات درج ذیل ہیں (64 بٹ اسی طرح کی ہے):

| جدول 6.49.1 32 بٹ کمپیوٹر کے لیے اے آر ایم ویکٹر استثنیٰ/انٹرپٹ |

|||

|---|---|---|---|

| استثناء/ خلل | چھوٹا ہاتھ | پتہ | اعلیٰ خطاب |

| دوبارہ ترتیب دیں۔ | ری سیٹ کریں۔ | 0x00000000 | 0xffff0000 |

| غیر متعینہ ہدایات | UNDEF | 0x00000004 | 0xffff0004 |

| سافٹ ویئر انٹرپٹ | SWI | 0x00000008 | 0xffff0008 |

| پری فیچ اسقاط | pabt | 0x0000000C | 0xffff000C |

| اسقاط حمل کی تاریخ | ڈی اے بی ٹی | 0x00000010 | 0xffff0010 |

| محفوظ | - | 0x00000014 | 0xffff0014 |

| مداخلت کی درخواست | IRQ | 0x00000018 | 0xffff0018 |

| فاسٹ مداخلت کی درخواست | ایف آئی کیو | 0x0000001C | 0xffff001C |

یہ 6502 فن تعمیر کے انتظام کی طرح لگتا ہے جہاں این ایم آئی , بی آر ، اور IRQ صفحہ صفر میں پوائنٹر ہوسکتے ہیں، اور متعلقہ معمولات میموری (ROM OS) میں زیادہ ہوتے ہیں۔ پچھلے جدول کی قطاروں کی مختصر تفصیل حسب ذیل ہے:

ری سیٹ کریں۔

ایسا اس وقت ہوتا ہے جب پروسیسر پاور اپ ہوتا ہے۔ یہ سسٹم کو شروع کرتا ہے اور مختلف پروسیسر موڈز کے لیے اسٹیکس سیٹ کرتا ہے۔ یہ سب سے زیادہ ترجیحی استثناء ہے۔ ری سیٹ ہینڈلر میں داخل ہونے پر، CPSR SVC موڈ میں ہوتا ہے اور IRQ اور FIQ دونوں بٹس 1 پر سیٹ ہوتے ہیں، کسی بھی رکاوٹ کو چھپاتے ہیں۔

اسقاط حمل کی تاریخ

دوسری اعلی ترین ترجیح۔ ایسا اس وقت ہوتا ہے جب ہم کسی غلط ایڈریس کو پڑھنے/لکھنے کی کوشش کرتے ہیں یا رسائی کی غلط اجازت حاصل کرتے ہیں۔ ڈیٹا ایبورٹ ہینڈلر میں داخل ہونے پر، IRQs کو غیر فعال کر دیا جائے گا (I-bit سیٹ 1) اور FIQ کو فعال کر دیا جائے گا۔ IRQs نقاب پوش ہیں، لیکن FIQs کو بے نقاب رکھا گیا ہے۔

ایف آئی کیو

سب سے زیادہ ترجیحی مداخلت، IRQ اور FIQs، FIQ کو سنبھالنے تک غیر فعال کر دیے جاتے ہیں۔

IRQ

اعلی ترجیحی مداخلت، IRQ ہینڈلر، صرف اس صورت میں داخل کیا جاتا ہے جب کوئی جاری FIQ اور ڈیٹا اسقاط نہ ہو۔

پری فیچ اسقاط

یہ ڈیٹا اسقاط کی طرح ہے لیکن پتہ کی بازیافت میں ناکامی پر ہوتا ہے۔ ہینڈلر میں داخل ہونے پر، IRQs کو غیر فعال کر دیا جاتا ہے لیکن FIQs فعال رہتے ہیں اور پری فیچ اسقاط کے دوران ہو سکتے ہیں۔

SWI

ایک سافٹ ویئر انٹرپٹ (SWI) استثناء اس وقت ہوتا ہے جب SWI ہدایات پر عمل کیا جاتا ہے اور دیگر اعلی ترجیحی استثناء میں سے کسی کو پرچم نہیں لگایا گیا ہے۔

غیر متعینہ ہدایات

غیر متعینہ ہدایات کی استثناء اس وقت ہوتی ہے جب کوئی ہدایت جو ARM یا انگوٹھے کے انسٹرکشن سیٹ میں نہیں ہے پائپ لائن کے عمل کے مرحلے تک پہنچ جاتی ہے اور دیگر استثناء میں سے کسی کو بھی جھنڈا نہیں لگایا گیا ہے۔ یہ وہی ترجیح ہے جو SWI کی ہے جو ایک وقت میں ہو سکتی ہے۔ اس کا مطلب یہ ہے کہ جس ہدایات پر عمل کیا جا رہا ہے وہ ایک ہی وقت میں SWI ہدایات اور غیر متعینہ ہدایات دونوں نہیں ہو سکتے۔

ARM استثناء ہینڈلنگ

مندرجہ ذیل واقعات رونما ہوتے ہیں جب کوئی استثناء ہوتا ہے:

- CPSR کو استثناء موڈ کے SPSR میں اسٹور کریں۔

- PC استثناء موڈ کے LR میں محفوظ ہے۔

- لنک رجسٹر کو موجودہ ہدایات کی بنیاد پر ایک مخصوص پتہ پر سیٹ کیا گیا ہے۔ مثال کے طور پر: ISR کے لیے، LR = آخری عمل میں آنے والی ہدایات + 8۔

- استثنا کے بارے میں CPSR کو اپ ڈیٹ کریں۔

- پی سی کو استثنیٰ ہینڈلر کے پتے پر سیٹ کریں۔

6.5 ہدایات اور ڈیٹا

ڈیٹا سے مراد متغیرات (ان کی اقدار کے ساتھ لیبلز) اور ارے اور دیگر ڈھانچے ہیں جو صف سے ملتے جلتے ہیں۔ تار حروف کی ایک صف کی طرح ہے۔ پچھلے ابواب میں سے ایک میں عدد کی ایک صف نظر آتی ہے۔ ہدایات opcodes اور ان کے کاموں کا حوالہ دیتے ہیں۔ ایک پروگرام کو میموری کے ایک جاری حصے میں ملا کر اوپکوڈز اور ڈیٹا کے ساتھ لکھا جا سکتا ہے۔ اس نقطہ نظر کے نقصانات ہیں لیکن اس کی سفارش نہیں کی جاتی ہے۔

ایک پروگرام کو پہلے ہدایات کے ساتھ لکھا جانا چاہیے، اس کے بعد ڈیٹا (ڈیٹم کی جمع ڈیٹا ہے)۔ ہدایات اور ڈیٹا کے درمیان علیحدگی صرف چند بائٹس ہو سکتی ہے۔ ایک پروگرام کے لیے، ہدایات اور ڈیٹا دونوں میموری میں ایک یا دو الگ الگ حصوں میں ہو سکتے ہیں۔

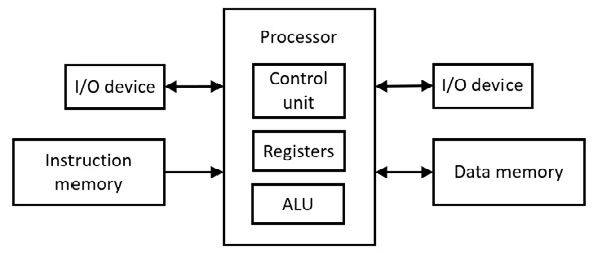

6.6 ہارورڈ فن تعمیر

ابتدائی کمپیوٹرز میں سے ایک ہارورڈ مارک I (1944) کہلاتا ہے۔ ہارورڈ کا ایک سخت فن تعمیر پروگرام کی ہدایات کے لیے ایک ایڈریس اسپیس اور ڈیٹا کے لیے الگ الگ ایڈریس اسپیس کا استعمال کرتا ہے۔ اس کا مطلب ہے کہ دو الگ الگ یادیں ہیں۔ مندرجہ ذیل فن تعمیر کو ظاہر کرتا ہے:

شکل 6.71 ہارورڈ آرکیٹیکچر

کنٹرول یونٹ ہدایات کی ضابطہ کشائی کرتا ہے۔ ریاضی منطقی یونٹ (ALU) ریاضی کی کارروائیاں امتزاج منطق (گیٹس) کے ساتھ کرتا ہے۔ ALU منطقی کارروائیاں بھی کرتا ہے (جیسے شفٹنگ)۔

6502 مائیکرو پروسیسر کے ساتھ، ایک ہدایت مائیکرو پروسیسر کو سب سے پہلے (کنٹرول یونٹ) کو جاتی ہے اس سے پہلے کہ ڈیٹام (ڈیٹا کے لیے واحد) µP رجسٹر میں آپس میں بات چیت کرنے سے پہلے۔ اس کے لیے کم از کم دو گھڑی کی دالیں درکار ہیں اور یہ ہدایات اور ڈیٹم تک بیک وقت رسائی نہیں ہے۔ دوسری طرف، ہارورڈ فن تعمیر ہدایات اور ڈیٹا تک بیک وقت رسائی فراہم کرتا ہے، جس میں ہدایات اور ڈیٹم دونوں ایک ہی وقت میں µP میں داخل ہوتے ہیں (اوپکوڈ ٹو کنٹرول یونٹ اور ڈیٹم ٹو µP رجسٹر)، کم از کم ایک گھڑی کی نبض کی بچت کرتے ہیں۔ یہ متوازی کی ایک شکل ہے۔ متوازی کی یہ شکل جدید مدر بورڈز میں ہارڈ ویئر کیشے میں استعمال ہوتی ہے (مندرجہ ذیل بحث کو دیکھیں)۔

6.7 کیشے میموری

Cache Memory (RAM) ایک تیز رفتار میموری کا علاقہ ہے (مین میموری کی رفتار کے مقابلے میں) جو مستقبل کے استعمال کے لیے پروگرام کی ہدایات یا ڈیٹا کو عارضی طور پر محفوظ کرتا ہے۔ کیش میموری مین میموری سے زیادہ تیزی سے کام کرتی ہے۔ عام طور پر، یہ ہدایات یا ڈیٹا آئٹمز حالیہ مین میموری سے حاصل کیے جاتے ہیں اور جلد ہی دوبارہ ضرورت پڑنے کا امکان ہے۔ کیش میموری کا بنیادی مقصد ایک ہی مرکزی میموری کے مقامات تک بار بار رسائی کی رفتار کو بڑھانا ہے۔ مؤثر ہونے کے لیے، کیش شدہ آئٹمز تک رسائی ان ہدایات یا ڈیٹا کے اصل ماخذ تک رسائی سے کہیں زیادہ تیز ہونی چاہیے جسے بیکنگ اسٹور کہا جاتا ہے۔

جب کیشنگ استعمال میں ہو تو، میموری کے مرکزی مقام تک رسائی کی ہر کوشش کیش کی تلاش سے شروع ہوتی ہے۔ اگر مطلوبہ آئٹم موجود ہے تو، پروسیسر اسے فوری طور پر بازیافت کرتا ہے اور استعمال کرتا ہے۔ اسے کیشے ہٹ کہتے ہیں۔ اگر کیشے کی تلاش ناکام ہو جاتی ہے (کیشے کی کمی)، ہدایات یا ڈیٹا آئٹم کو بیکنگ اسٹور (مین میموری) سے بازیافت کرنا ضروری ہے۔ درخواست کردہ آئٹم کی بازیافت کے عمل میں، مستقبل قریب میں متوقع استعمال کے لیے کیشے میں ایک کاپی شامل کی جاتی ہے۔

میموری مینجمنٹ یونٹ

میموری مینجمنٹ یونٹ (MMU) ایک سرکٹ ہے جو مدر بورڈ پر مرکزی میموری اور متعلقہ میموری رجسٹر کا انتظام کرتا ہے۔ ماضی میں، یہ مدر بورڈ پر ایک الگ مربوط سرکٹ تھا۔ لیکن آج، یہ عام طور پر مائکرو پروسیسر کا حصہ ہے۔ ایم ایم یو کو کیشے (سرکٹ) کا بھی انتظام کرنا چاہیے جو آج مائیکرو پروسیسر کا بھی ایک حصہ ہے۔ کیش سرکٹ ماضی میں ایک الگ مربوط سرکٹ ہے۔

جامد رام

جامد RAM (SRAM) کے پاس DRAM کے مقابلے میں کافی تیزی سے رسائی کا وقت ہے، اگرچہ نمایاں طور پر زیادہ پیچیدہ سرکٹری کی قیمت پر۔ SRAM بٹ سیلز انٹیگریٹڈ سرکٹ ڈائی پر DRAM ڈیوائس کے سیلز کے مقابلے میں بہت زیادہ جگہ لیتے ہیں جو ڈیٹا کی مساوی مقدار کو ذخیرہ کرنے کے قابل ہے۔ مین میموری (RAM) عام طور پر DRAM (ڈائنامک RAM) پر مشتمل ہوتی ہے۔

کیش میموری کمپیوٹر کی کارکردگی کو بہتر بناتی ہے کیونکہ بہت سے الگورتھم جو آپریٹنگ سسٹمز اور ایپلی کیشنز کے ذریعہ چلائے جاتے ہیں حوالہ کی جگہ کو ظاہر کرتے ہیں۔ Locality of Reference سے مراد ڈیٹا کا دوبارہ استعمال ہے جس تک حال ہی میں رسائی حاصل کی گئی ہے۔ اسے Temporal Locality کہا جاتا ہے۔ جدید مدر بورڈ پر، کیش میموری مائکرو پروسیسر کی طرح انٹیگریٹڈ سرکٹ میں ہے۔ مین میموری (DRAM) دور ہے اور بسوں کے ذریعے قابل رسائی ہے۔ حوالہ کے محل وقوع سے بھی مقامی علاقہ مراد ہے۔ مقامی علاقے کا تعلق جسمانی قربت کی وجہ سے ڈیٹا تک رسائی کی تیز رفتار سے ہے۔

ایک اصول کے طور پر، بیکنگ اسٹور (مین میموری) کے مقابلے میں کیش میموری کے علاقے چھوٹے ہیں (بائٹ مقامات کی تعداد میں)۔ کیش میموری ڈیوائسز کو زیادہ سے زیادہ رفتار کے لیے ڈیزائن کیا گیا ہے جس کا عام طور پر مطلب یہ ہے کہ وہ بیکنگ اسٹور میں استعمال ہونے والی ڈیٹا اسٹوریج ٹیکنالوجی کے مقابلے زیادہ پیچیدہ اور مہنگے ہیں۔ ان کے محدود سائز کی وجہ سے، کیش میموری آلات تیزی سے بھر جاتے ہیں۔ جب کسی کیشے میں نئی اندراج کو ذخیرہ کرنے کے لیے کوئی جگہ دستیاب نہیں ہوتی ہے، تو ایک پرانی اندراج کو ضائع کر دینا چاہیے۔ کیش کنٹرولر ایک کیشے کی تبدیلی کی پالیسی کا استعمال کرتا ہے یہ منتخب کرنے کے لیے کہ کون سی کیش انٹری کو نئے اندراج کے ذریعے اوور رائٹ کیا جائے گا۔

مائیکرو پروسیسر کیش میموری کا مقصد وقت کے ساتھ ساتھ کیش ہٹ کے فیصد کو زیادہ سے زیادہ کرنا ہے، اس طرح ہدایات پر عمل درآمد کی بلند ترین شرح فراہم کرتا ہے۔ اس مقصد کو حاصل کرنے کے لیے، کیشنگ منطق کو یہ تعین کرنا چاہیے کہ کون سی ہدایات اور ڈیٹا کو کیش میں رکھا جائے گا اور مستقبل قریب میں استعمال کے لیے برقرار رکھا جائے گا۔

ایک پروسیسر کی کیشنگ منطق میں اس بات کی یقین دہانی نہیں ہوتی کہ کیشڈ ڈیٹا آئٹم کو کیش میں داخل کرنے کے بعد اسے دوبارہ استعمال کیا جائے گا۔

کیشنگ کی منطق اس امکان پر انحصار کرتی ہے کہ عارضی (وقت کے ساتھ دہرانے) اور مقامی (اسپیس) لوکلٹی کی وجہ سے، مستقبل قریب میں کیش شدہ ڈیٹا تک رسائی کا ایک بہت اچھا موقع ہے۔ جدید پروسیسرز پر عملی نفاذ میں، کیشے ہٹ عام طور پر 95 سے 97 فیصد میموری تک رسائی پر ہوتی ہے۔ چونکہ کیش میموری کی لیٹنسی DRAM کی لیٹنسی کا ایک چھوٹا سا حصہ ہے، اس لیے کیش فری ڈیزائن کے مقابلے میں ہائی کیش ہٹ ریٹ کارکردگی میں خاطر خواہ بہتری کا باعث بنتا ہے۔

کیشے کے ساتھ کچھ ہم آہنگی۔

جیسا کہ پہلے ذکر کیا گیا ہے، میموری میں ایک اچھے پروگرام میں ہدایات کو ڈیٹا سے الگ کیا جاتا ہے۔ کچھ کیش سسٹمز میں، پروسیسر کے 'بائیں' پر ایک کیش سرکٹ ہوتا ہے اور پروسیسر کے 'دائیں' پر ایک اور کیش سرکٹ ہوتا ہے۔ بائیں کیش پروگرام (یا ایپلیکیشن) کی ہدایات کو سنبھالتا ہے اور دائیں کیش اسی پروگرام (یا اسی ایپلی کیشن) کے ڈیٹا کو ہینڈل کرتا ہے۔ یہ ایک بہتر اضافہ کی رفتار کی طرف جاتا ہے.

6.8 پروسیس اور تھریڈز

CISC اور RISC دونوں کمپیوٹرز کے عمل ہوتے ہیں۔ سافٹ ویئر پر ایک عمل جاری ہے۔ ایک پروگرام جو چل رہا ہے (عمل درآمد) ایک عمل ہے۔ آپریٹنگ سسٹم اپنے پروگراموں کے ساتھ آتا ہے۔ جب کمپیوٹر کام کر رہا ہوتا ہے تو آپریٹنگ سسٹم کے وہ پروگرام بھی چل رہے ہوتے ہیں جو کمپیوٹر کو کام کرنے کے قابل بناتے ہیں۔ یہ آپریٹنگ سسٹم کے عمل ہیں۔ صارف یا پروگرامر اپنے پروگرام خود لکھ سکتا ہے۔ جب صارف کا پروگرام چل رہا ہے، تو یہ ایک عمل ہے۔ اس سے کوئی فرق نہیں پڑتا کہ پروگرام اسمبلی زبان میں لکھا گیا ہے یا اعلیٰ سطحی زبان جیسے C یا C++ میں۔ تمام عمل (صارف یا OS) کو ایک اور عمل کے ذریعے منظم کیا جاتا ہے جسے 'شیڈیولر' کہا جاتا ہے۔

ایک دھاگہ ایک عمل سے تعلق رکھنے والے ذیلی عمل کی طرح ہے۔ ایک عمل شروع ہو سکتا ہے اور دھاگوں میں تقسیم ہو سکتا ہے اور پھر بھی ایک عمل کے طور پر جاری رہتا ہے۔ دھاگوں کے بغیر عمل کو مرکزی دھاگے کے طور پر سمجھا جا سکتا ہے۔ عمل اور ان کے دھاگوں کا انتظام ایک ہی شیڈیولر کے ذریعے کیا جاتا ہے۔ شیڈولر خود ایک پروگرام ہے جب یہ OS ڈسک میں رہائشی ہے۔ میموری میں چلتے وقت، شیڈولر ایک عمل ہوتا ہے۔

6.9 ملٹی پروسیسنگ

دھاگوں کا انتظام تقریباً عمل کی طرح ہوتا ہے۔ ملٹی پروسیسنگ کا مطلب ہے ایک ہی وقت میں ایک سے زیادہ عمل چلانا۔ صرف ایک مائکرو پروسیسر والے کمپیوٹر ہیں۔ ایک سے زیادہ مائکرو پروسیسر والے کمپیوٹر ہیں۔ ایک مائیکرو پروسیسر کے ساتھ، عمل اور/یا تھریڈز ایک ہی مائکرو پروسیسر کو انٹرلیونگ (یا ٹائم سلائسنگ) طریقے سے استعمال کرتے ہیں۔ اس کا مطلب یہ ہے کہ ایک عمل پروسیسر کا استعمال کرتا ہے اور ختم کیے بغیر رک جاتا ہے۔ ایک اور عمل یا تھریڈ پروسیسر کا استعمال کرتا ہے اور ختم کیے بغیر رک جاتا ہے۔ پھر، ایک اور عمل یا دھاگہ مائکرو پروسیسر کا استعمال کرتا ہے اور ختم کیے بغیر رک جاتا ہے۔ یہ اس وقت تک جاری رہتا ہے جب تک کہ شیڈیولر کے ذریعہ قطار میں لگائے گئے تمام عمل اور دھاگوں میں پروسیسر کا حصہ نہ ہو۔ اسے کنکرنٹ ملٹی پروسیسنگ کہا جاتا ہے۔

جب ایک سے زیادہ مائیکرو پروسیسر ہوتے ہیں، تو ایک متوازی ملٹی پروسیسنگ ہوتی ہے، جیسا کہ ہم آہنگی کے برخلاف ہوتا ہے۔ اس صورت میں، ہر پروسیسر ایک خاص عمل یا دھاگہ چلاتا ہے، جو دوسرے پروسیسر کے چلانے سے مختلف ہے۔ ایک ہی مدر بورڈ پر تمام پروسیسرز متوازی ملٹی پروسیسنگ میں ایک ہی وقت میں اپنے مختلف عمل اور/یا مختلف تھریڈز چلاتے ہیں۔ متوازی ملٹی پروسیسنگ میں عمل اور دھاگوں کا انتظام ابھی بھی شیڈیولر کے ذریعہ کیا جاتا ہے۔ متوازی ملٹی پروسیسنگ کنکرنٹ ملٹی پروسیسنگ سے تیز ہے۔

اس مقام پر، قاری سوچ سکتا ہے کہ متوازی پروسیسنگ کنکرنٹ پروسیسنگ سے کتنی تیز ہے۔ اس کی وجہ یہ ہے کہ پروسیسرز ایک ہی میموری اور ان پٹ/آؤٹ پٹ پورٹس کا اشتراک کرتے ہیں (مختلف اوقات میں استعمال کرنا پڑتا ہے۔ ٹھیک ہے، کیشے کے استعمال سے، مدر بورڈ کا مجموعی آپریشن تیز تر ہوتا ہے۔

6.10 صفحہ بندی

میموری مینجمنٹ یونٹ (MMU) ایک سرکٹ ہے جو مائکرو پروسیسر کے قریب یا مائکرو پروسیسر چپ میں ہوتا ہے۔ یہ میموری میپ یا پیجنگ اور میموری کے دیگر مسائل کو ہینڈل کرتا ہے۔ نہ ہی 6502 µP اور نہ ہی کموڈور-64 کمپیوٹر میں ایک MMU فی سی ہے (حالانکہ کموڈور-64 میں ابھی بھی کچھ میموری کا انتظام موجود ہے)۔ کموڈور-64 صفحہ بندی کے ذریعے میموری کو سنبھالتا ہے جہاں ہر صفحہ 256 ہے۔ 10 بائٹس لمبا (100 16 بائٹس لمبا)۔ صفحہ بندی کرکے یادداشت کو سنبھالنا اس کے لیے واجب نہیں تھا۔ اس میں اب بھی صرف میموری کا نقشہ اور پھر ایسے پروگرام ہوسکتے ہیں جو صرف اپنے آپ کو ان کے مختلف نامزد علاقوں میں فٹ کرتے ہیں۔ ٹھیک ہے، صفحہ بندی میموری کا موثر استعمال فراہم کرنے کا ایک طریقہ ہے جس میں میموری کے بہت سے حصے ہیں جن میں ڈیٹا یا پروگرام نہیں ہوسکتا ہے۔

x86 386 کمپیوٹر آرکیٹیکچر 1985 میں جاری کیا گیا تھا۔ ایڈریس بس 32 بٹ چوڑی ہے۔ تو کل 2 32 = 4,294,967,296 پتہ کی جگہ ممکن ہے۔ یہ پتہ کی جگہ 1,048,576 صفحات = 1,024 KB صفحات میں تقسیم ہے۔ صفحات کی اس تعداد کے ساتھ، ایک صفحہ 4,096 بائٹس = 4 KB پر مشتمل ہے۔ درج ذیل جدول x86 32 بٹ فن تعمیر کے لیے جسمانی ایڈریس کے صفحات دکھاتا ہے:

| جدول 6.10.1 x86 فن تعمیر کے لیے فزیکل ایڈریس ایبل پیجز |

||

|---|---|---|

| بیس 16 پتے | صفحات | بیس 10 پتے |

| FFFFF000 - FFFFFFFF | صفحہ 1,048,575 | 4,294,963,200 - 4,294,967,295 |

| FFFFE000 - FFFFFEFFF | صفحہ 1,044,479 | 4,294,959,104 - 4,294,963,199 |

| FFFFD000 - FFFFDFFF | صفحہ 1,040,383 | 4,294,955,008 - 4,294,959,103 |

| | | | |

| | | |

| | | |

| 00002000 - 00002FFF | صفحہ 2 | 8,192 – 12,288 |

| 00001000 - 00001FFF | صفحہ 1 | 4,096 – 8,191 |

| 00000000 - 00000FFF | صفحہ 0 | 0 - 4,095 |

آج ایک درخواست ایک سے زیادہ پروگراموں پر مشتمل ہے۔ ایک پروگرام ایک صفحے سے کم لے سکتا ہے (4096 سے کم) یا یہ دو یا زیادہ صفحات لے سکتا ہے۔ لہذا، ایک درخواست ایک یا زیادہ صفحات لے سکتی ہے جہاں ہر صفحہ 4096 بائٹس لمبا ہوتا ہے۔ مختلف لوگ ایک درخواست لکھ سکتے ہیں، جس میں ہر فرد کو ایک یا زیادہ صفحات تفویض کیے گئے ہیں۔

نوٹ کریں کہ صفحہ 0 00000000H سے 00000FFF تک ہے

صفحہ 1 00001000H سے 00001FFFH تک ہے، صفحہ 2 00002000 سے ہے ایچ - 00002FFF ایچ ، اور اسی طرح. 32 بٹ کمپیوٹر کے لیے، فزیکل پیج ایڈریسنگ کے لیے پروسیسر میں دو 32 بٹ رجسٹر ہوتے ہیں: ایک بیس ایڈریس کے لیے اور دوسرا انڈیکس ایڈریس کے لیے۔ صفحہ 2 کے بائٹ مقامات تک رسائی حاصل کرنے کے لیے، مثال کے طور پر، بیس ایڈریس کے لیے رجسٹر 00002 ہونا چاہیے۔ ایچ جو کہ صفحہ 2 کے ابتدائی پتوں کے لیے پہلے 20 بٹس (بائیں سے) ہیں۔ باقی بٹس 000 کی رینج میں ہیں۔ ایچ FFF کو ایچ رجسٹر میں ہیں جسے 'انڈیکس رجسٹر' کہا جاتا ہے۔ لہذا، صفحہ میں موجود تمام بائٹس کو صرف 000 سے انڈیکس رجسٹر میں مواد کو بڑھا کر حاصل کیا جا سکتا ہے۔ ایچ FFF کو ایچ . انڈیکس رجسٹر میں مواد کو اس مواد میں شامل کیا جاتا ہے جو مؤثر پتہ حاصل کرنے کے لیے بیس رجسٹر میں تبدیل نہیں ہوتا ہے۔ یہ انڈیکس ایڈریسنگ سکیم دوسرے صفحات کے لیے درست ہے۔

تاہم، ایسا نہیں ہے کہ ہر صفحے کے لیے اسمبلی لینگوئج پروگرام کیسے لکھا جاتا ہے۔ ہر صفحہ کے لیے، پروگرامر صفحہ 000 سے شروع ہونے والا کوڈ لکھتا ہے۔ ایچ صفحہ FFF پر ایچ . چونکہ مختلف صفحات میں کوڈ جڑے ہوئے ہیں، اس لیے مرتب کرنے والا انڈیکس ایڈریسنگ کا استعمال کرتا ہے تاکہ مختلف صفحات میں تمام متعلقہ پتوں کو جوڑ سکے۔ مثال کے طور پر، یہ فرض کرتے ہوئے کہ صفحہ 0، صفحہ 1، اور صفحہ 2 ایک درخواست کے لیے ہیں اور ہر ایک میں 555 ہے ایچ ایڈریس جو ایک دوسرے سے جڑا ہوا ہے، مرتب کرنے والا اس طرح سے مرتب کرتا ہے کہ جب 555 ایچ صفحہ 0 تک رسائی حاصل کرنا ہے، 00000 ایچ بیس رجسٹر اور 555 میں ہوگا۔ ایچ انڈیکس رجسٹر میں ہوگا۔ جب 555 ایچ صفحہ 1 تک رسائی حاصل کرنا ہے، 00001 ایچ بیس رجسٹر اور 555 میں ہوگا۔ ایچ انڈیکس رجسٹر میں ہوگا۔ جب 555 ایچ صفحہ 2 تک رسائی حاصل کرنا ہے، 00002 ایچ بیس رجسٹر میں ہوگا اور 555H انڈیکس رجسٹر میں ہوگا۔ یہ ممکن ہے کیونکہ پتوں کی شناخت لیبلز (متغیرات) کے ذریعے کی جا سکتی ہے۔ مختلف پروگرامرز کو مختلف مربوط پتوں کے لیے استعمال کیے جانے والے لیبلز کے نام پر متفق ہونا پڑتا ہے۔

صفحہ ورچوئل میموری

صفحہ بندی، جیسا کہ پہلے بیان کیا گیا ہے، ایک تکنیک میں میموری کے سائز کو بڑھانے کے لیے ترمیم کی جا سکتی ہے جسے 'پیج ورچوئل میموری' کہا جاتا ہے۔ یہ فرض کرتے ہوئے کہ تمام فزیکل میموری پیجز، جیسا کہ پہلے بیان کیا گیا ہے، کچھ نہ کچھ (ہدایات اور ڈیٹا) رکھتے ہیں، فی الحال تمام صفحات فعال نہیں ہیں۔ وہ صفحات جو فی الحال فعال نہیں ہیں ہارڈ ڈسک پر بھیجے جاتے ہیں اور ان کی جگہ ہارڈ ڈسک کے صفحات لے جاتے ہیں جن کو چلانے کی ضرورت ہوتی ہے۔ اس طرح یادداشت کا سائز بڑھ جاتا ہے۔ جیسے جیسے کمپیوٹر کام کرتا رہتا ہے، غیر فعال ہونے والے صفحات ہارڈ ڈسک میں موجود صفحات کے ساتھ تبدیل ہو جاتے ہیں جو اب بھی وہ صفحات ہو سکتے ہیں جو میموری سے ڈسک پر بھیجے گئے تھے۔ یہ سب میموری مینجمنٹ یونٹ (MMU) کرتا ہے۔

6.11 مسائل

قارئین کو مشورہ دیا جاتا ہے کہ اگلے باب میں جانے سے پہلے ایک باب میں تمام مسائل حل کر لیں۔

1) CISC اور RISC کمپیوٹر فن تعمیر کی مماثلت اور فرق بتائیں۔ SISC اور RISC کمپیوٹر میں سے ایک ایک مثال کا نام دیں۔

2) a) بٹس کے لحاظ سے CISC کمپیوٹر کے درج ذیل نام کیا ہیں: بائٹ، ورڈ، ڈبل ورڈ، کواڈ ورڈ، اور ڈبل کواڈ ورڈ۔

ب) بٹس کے لحاظ سے RISC کمپیوٹر کے درج ذیل نام کیا ہیں: بائٹ، ہاف ورڈ، ورڈ، اور ڈبل ورڈ۔

ج) ہاں یا نہیں۔ کیا ڈبل ورڈ اور کواڈ ورڈ دونوں CISC اور RISC فن تعمیر میں ایک جیسے ہیں

3 a) x64 کے لیے، اسمبلی لینگویج ہدایات کے لیے بائٹس کی تعداد کس چیز سے ہوتی ہے؟

b) کیا ARM 64 کے لیے اسمبلی کی تمام زبانی ہدایات کے لیے بائٹس کی تعداد مقرر ہے؟ اگر ہاں، تمام ہدایات کے لیے بائٹس کی تعداد کیا ہے؟

4) x64 اور ان کے معانی کے لیے سب سے زیادہ استعمال ہونے والی اسمبلی زبان کی ہدایات کی فہرست بنائیں۔

5) ARM 64 کے لیے سب سے زیادہ استعمال ہونے والی اسمبلی لینگویج ہدایات اور ان کے معنی درج کریں۔

6) پرانے کمپیوٹر ہارورڈ آرکیٹیکچر کا لیبل لگا بلاک ڈایاگرام بنائیں۔ اس کی ہدایات اور ڈیٹا فیچرز کو جدید کمپیوٹرز کے کیش میں کس طرح استعمال کیا جاتا ہے اس کی وضاحت کریں۔

7) کسی عمل اور تھریڈ کے درمیان فرق کریں اور اس عمل کا نام بتائیں جو زیادہ تر کمپیوٹر سسٹمز میں پروسیس اور تھریڈز کو ہینڈل کرتا ہے۔

8) مختصراً وضاحت کریں کہ ملٹی پروسیسنگ کیا ہے۔

9) a) صفحہ بندی کی وضاحت کریں جیسا کہ x86 386 µP کمپیوٹر فن تعمیر پر لاگو ہوتا ہے۔

ب) پوری میموری کے سائز کو بڑھانے کے لیے اس پیجنگ کو کیسے تبدیل کیا جا سکتا ہے؟